基于VHDL的多功能可變模計數(shù)器設計方案

0 引 言

隨著電子技術、計算機技術和EDA技術的不斷發(fā)展,利用FPGA/CPLD進行數(shù)字系統(tǒng)的開發(fā)已被廣泛應用于通信、航天、

QuartusⅡ是Altera公司在21世紀初推出的FPGA/CPLD集成開發(fā)環(huán)境,是Altera公司前一代FPGA/CPLD集成開發(fā)環(huán)境Max+PlusⅡ的更新?lián)Q代產(chǎn)品,其界面友好,使用便捷,功能強大,為設計者提供了一種與結構無關的設計環(huán)境,使設計者能方便地進行設計輸入、快速處理和器件編程。

計數(shù)器是數(shù)字系統(tǒng)中使用最多的時序電路之一,不僅能用于對時鐘脈沖計數(shù),還可以用于分頻、定時、產(chǎn)生節(jié)拍脈沖和脈沖序列以及進行數(shù)字運算等。可變模計數(shù)器由于計數(shù)容量可以根據(jù)需要進行變化,為其廣泛使用創(chuàng)造了便利。這里在QuartusⅡ開發(fā)環(huán)境下,用VHDL語言設計了一種具有清零、置數(shù)、使能控制、可逆計數(shù)和可變模功能的計數(shù)器。

1 基本可變模計數(shù)器設計

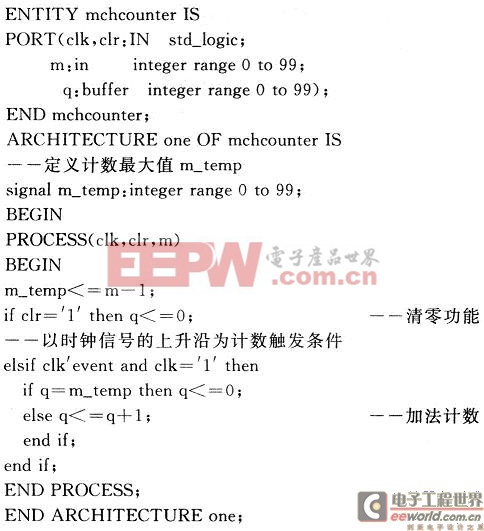

可變模計數(shù)器是指計數(shù)/模值可根據(jù)需要進行變化的計數(shù)器。電路符號圖1所示,clk為時鐘脈沖輸入端,clr為清零端,m為模值輸入端,q為計數(shù)輸出端。

基本可變模計數(shù)器的VHDL代碼如下所示:

說明:上述代碼設計采用了常用的if語句結構,即“if條件句then順序語句elsif條件句then順序語句else順序語句end if”結構,實現(xiàn)模值小于99的可變模計數(shù)。

塵埃粒子計數(shù)器相關文章:塵埃粒子計數(shù)器原理

評論