基于FPGA的磁浮軸承控制系統(tǒng)的設(shè)計(jì)與研究

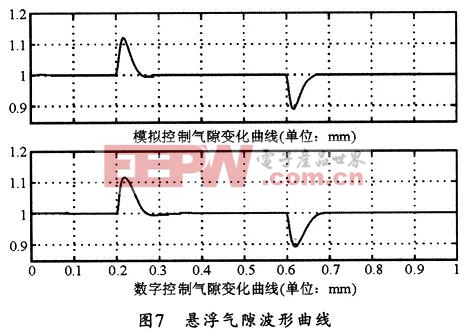

加載/減載可使用Flux*來描述,用以表示在0.2 s和0.6 s時(shí)刻階躍加載和減載400N。其仿真結(jié)果如圖7所示,所得到的懸浮氣隙波形曲線中的上方為模擬控制,下方為數(shù)字控制。

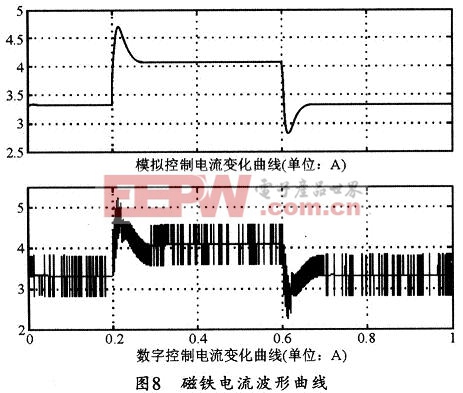

電流輸出結(jié)果要縮小1000倍,圖8所示是其磁鐵電流曲線(單位A),其中實(shí)際額定電流值設(shè)定為3.3 A。上方為模擬控制,下方為數(shù)字控制。

4 硬件協(xié)同仿真

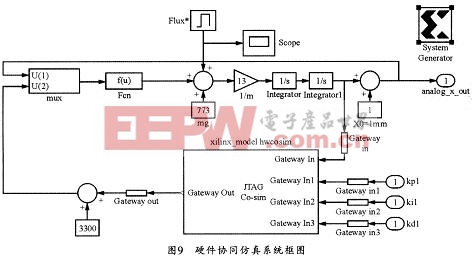

硬件協(xié)同仿真就是在對(duì)Matlab—Simulink環(huán)境下所設(shè)計(jì)的算法模型進(jìn)行仿真后,“System Gen-erator”可以結(jié)合實(shí)際“Xilinx—FPGA”的硬件資源生成一個(gè)集成有該算法的“硬核”;然后通過FPGA把“硬核”下載至FPGA中。最后以同樣的信號(hào)作為輸入,一路信號(hào)接“軟件算法模型”,一路信號(hào)接“硬核”,同時(shí)觀測(cè)兩者的輸出。如果處理結(jié)果一致,則可證明Matlab—Simulink環(huán)境下所設(shè)計(jì)的

在對(duì)數(shù)字控制系統(tǒng)仿真運(yùn)行協(xié)同仿真之后,就會(huì)生成新的數(shù)字PID模塊。然后把它重新接入數(shù)字控制系統(tǒng)仿真框圖中,就會(huì)得到如圖9所示的硬件協(xié)同仿真系統(tǒng)框圖。

用圖5的理論控制與圖9進(jìn)行對(duì)比,然后連接開發(fā)板,打開電源,并運(yùn)行模型進(jìn)行仿真,則可從仿真波形中很明顯的看到,硬件協(xié)同仿真的結(jié)果和理論結(jié)果完全一樣。

5 結(jié)束語

本文采用System Generator對(duì)基于FPGA的磁浮軸承控制系統(tǒng)進(jìn)行了仿真,并將其下載到FP-GA開發(fā)板進(jìn)行硬件協(xié)同,結(jié)果證明,在加載/減載400N力時(shí),所設(shè)計(jì)的數(shù)字PID控制器能較好的完成對(duì)磁浮軸承系統(tǒng)的控制,并實(shí)現(xiàn)穩(wěn)定懸浮。

pid控制器相關(guān)文章:pid控制器原理

評(píng)論