對(duì)基于FPGA的高斯白噪聲發(fā)生器的研究與設(shè)計(jì)

0 引 言

現(xiàn)代通訊電子設(shè)備的抗干擾測(cè)試已經(jīng)成為必須的測(cè)試項(xiàng)目,主要的干擾類型為噪聲干擾。在通信信道測(cè)試和電子對(duì)抗領(lǐng)域里,噪聲始終是最基本、最常用的干擾源之一。如何產(chǎn)生穩(wěn)定和精確的噪聲信號(hào)已經(jīng)成為一個(gè)重要的研究領(lǐng)域。其中,帶限白噪聲信號(hào)時(shí)間相關(guān)性小,目前應(yīng)用最廣泛。現(xiàn)有的硬件高斯白噪聲發(fā)生器通常分為物理噪聲發(fā)生器和數(shù)字噪聲發(fā)生器兩類,數(shù)字噪聲發(fā)生器雖然沒(méi)有物理噪聲發(fā)生器的精度高,但是實(shí)現(xiàn)電路較為簡(jiǎn)單,易于應(yīng)用。

FPGA技術(shù)的發(fā)展,提高了硬件噪聲發(fā)生器的速度和性能,相比基于軟件實(shí)現(xiàn)的噪聲發(fā)生器,展現(xiàn)出更大的優(yōu)勢(shì)。本文設(shè)計(jì)的高斯白噪聲發(fā)生器采用FPGA的方式實(shí)現(xiàn),輸出的基帶白噪聲帶寬可調(diào),范圍為1~66 MHz,步進(jìn)3 MHz,幅度8位可調(diào),同時(shí)可產(chǎn)生正弦波、三角波、鋸齒波、方波等函數(shù)波,通過(guò)更改現(xiàn)場(chǎng)可編程器件的配置波形數(shù)據(jù)也可產(chǎn)生其他復(fù)雜函數(shù)波形。

l 高斯白噪聲發(fā)生器原理

本文所述的高斯白噪聲發(fā)生器如圖1所示。

首先,在現(xiàn)場(chǎng)可編程門陣列(Field Programmable Gate Array,FPGA)平臺(tái)上以一個(gè)統(tǒng)一的時(shí)鐘速度(以后稱之為噪聲發(fā)生速度,即f0)生成高速m序列偽隨機(jī)碼流,對(duì)該序列進(jìn)行有限沖擊響應(yīng)(Finite Impulse Response,F(xiàn)IR)數(shù)字濾波處理,得到帶限白噪聲數(shù)字序列,同時(shí)在FPGA中實(shí)現(xiàn)直接數(shù)字綜合(Direct Digital Synthesizer,DDS)算法,產(chǎn)生正弦數(shù)字序列,并與噪聲序列合成;其次,將以上得到的數(shù)字序列通過(guò)高速數(shù)/模

高斯白噪聲發(fā)生方法中涉及偽隨機(jī)碼發(fā)生算法、數(shù)字濾波算法和正弦波發(fā)生算法。本文詳細(xì)論述這幾種算法,及其在FPGA上的實(shí)現(xiàn)方法,分析了各種算法在頻域上的頻譜特性。

2 高斯白噪聲發(fā)生器算法分析

2.1 偽隨機(jī)碼發(fā)生算法

偽隨機(jī)碼(Pseudo-random Sequence,PS)的性能指標(biāo)直接影響產(chǎn)生白噪聲的隨機(jī)性,是系統(tǒng)設(shè)汁的關(guān)鍵。通常產(chǎn)生偽隨機(jī)碼的電路為一反饋移存器,分為線性和非線性兩類。前者產(chǎn)生周期最長(zhǎng)的二進(jìn)制數(shù)字序列為最大長(zhǎng)度線性反饋移存器序列,簡(jiǎn)稱m序列。本文采用的就是m序列偽隨機(jī)碼。

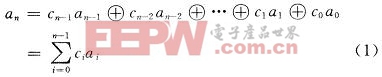

產(chǎn)生m序列的反饋移存器的遞推方程可以寫為:

它給出了移位輸入an與移位前各級(jí)狀態(tài)的關(guān)系。

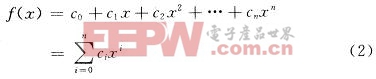

特征多項(xiàng)式寫為:

它決定了移位寄存器的反饋連接和序列的結(jié)構(gòu)。

m序列的自相關(guān)函數(shù)可表示為:

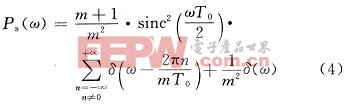

式(3)為一個(gè)周期(m=2n-1)內(nèi)的函數(shù),其中Tn為偽隨機(jī)噪聲碼元的寬度。整個(gè)時(shí)域的自相關(guān)函數(shù)的周期為m=2n-1。信號(hào)的自相關(guān)函數(shù)與功率譜密度構(gòu)成一對(duì)傅里葉變換,因此m序列的自相關(guān)函數(shù)經(jīng)過(guò)傅里葉變換,其功率譜密度為:

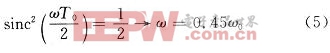

假定零頻處的功率為1,那么功率下降為0.5處的頻率為:

評(píng)論