AEMB軟核處理器的SoC系統驗證平臺的構建

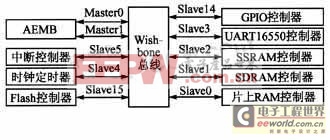

SoC系統中主要包含的IP模塊有:32位開源微處理器軟核AEMB、中斷控制器、時鐘定時器、Wishbone總線、片上RAM控制器、SDRAM控制器、SSRAM控制器、Flash控制器、UART16550控制器、GPIO控制器。整個SoC系統的總體結構如圖1所示。

圖1 SoC系統總體結構

為了方便后續開發與應用,本SoC系統中的Wishbone總線仲裁采用了開源的IP軟核wb_conmax。其為8×16的結構,即在該Wishbone總線模塊中可以使用8個主設備與16個從設備。本系統中使用了8個從設備接口和2個主設備接口。AEMB軟核中沒有提供時鐘定時器與中斷控制器,為了正常使用該軟核,本系統中加入了中斷控制器和時鐘定時器,這兩個控制器是作為從設備添加進來的。針對一些對存儲空間需求很少的應用,系統將片上RAM作為主存儲器。然而,FPGA片上存儲器的空間是非常有限的,為了能夠運行需要大量存儲空間的操作系統,以及讓系統正常上電啟動,就需要外部存儲器作為系統的主存儲器。所以,系統中還添加了SDRAM、SSRAM控制器及Flash存儲器。UART16550控制器和GPIO控制器作為2個從設備連接在系統中。

3 SoC系統驗證平臺具體構建

3.1 AEMB版本的選擇與配置

AEMB軟核采用最新的EDK62版本。本設計的目的在于整個SoC系統驗證平臺的構建,對微處理器性能及整個SoC系統的具體應用性能沒有要求。為了簡化設計,將AEMB軟核中可配置的一些優化選項全部禁掉。這樣不僅省去了對FPGA硬件邏輯資源的占用,而且也避免了因一些具體細節使用不當而帶來的諸多問題。

3.2 片上RAM的生成

為了減少對FPGA邏輯資源的占用,同時又能夠滿足最基本的啟動代碼的存放與運行,將片內存儲器的大小設為4 KB。使用Altera公司的FPGA開發環境QuartusII 9.0中的MegaWizard Plug-In Manager工具,來生成設定大小為4 KB的片上RAM。EDA開發工具生成的片上存儲文件僅是具有相關存儲器地址、數據及讀寫控制信號的一個HDL描述文件。為了能夠在本SoC系統中使用,需要將其包裝成符合Wishbone總線接口的一個從設備,以掛接在系統的Wishbone總線上。

3.3 片外存儲控制器的配置

在該SoC系統上,片外存儲控制器主要有SDRAM、Flash、SSRAM控制器。根據臺灣友晶公司的DE2-70開發板上實際存儲芯片的需要,對控制器的數據總線寬度與地址總線寬度作相應的修改與定制。一般情況下,SDRAM作為系統的主存儲器,Flash用來存儲系統的一些固化程序。在對一些實時系統進行時間參數測量的過程中,為了減小程序運行空間中時序的不穩定性影響,一般情況下測試程序都是在SSRAM器件中運行的。

作為存儲器件的物理芯片,數據總線的端口基本上都是雙向的,而在片內系統中數據端口基本上都是單向的。這些片外存儲控制器在進行物理板級的連接時需要對相應的數據端口作處理。以Flash控制器為例,數據總線的雙向I/O口具體實現RTL代碼如下:

其他的存儲器(如SDRAM、SSRAM)的數據總線雙向I/O的實現,也都是采用這種方法來完成的。

3.4 中斷控制器與時鐘定時器的配置

中斷控制器主要用于接收外部中斷源的中斷請求,并對中斷請求進行處理后再向CPU發出中斷請求,等待CPU響應中斷并進行處理。在CPU響應中斷的過程中,中斷控制器仍然負責管理外部中斷源的中斷請求,從而實現中斷的嵌套與禁止。在本設計中,中斷控制器的邏輯結構如圖2所示。所采用的中斷控制器主要負責接收片內IP核及片外器件所發出的中斷請求,然后根據一定的優先級與規則將中斷發送給微處理器。微處理器可以通過設置與讀取相應的中斷寄存器來管理查看中斷優先級與中斷狀態。

圖2 終端控制器邏輯結構

時鐘定時器主要是作為操作系統的時鐘滴答定時器,本質上就是一個簡單的計數器。在每個系統時鐘來到時計數器會自動加1,當計數器的值達到設定數值時便產生1次時鐘中斷。PTC是OpenCores組織發布的一個支持Wishbone總線接口的脈沖定時計數器。其不僅可以作為時鐘定時器,還可以通過配置寄存器的設置產生PWM脈沖輸出。本SoC系統中主要是使用PTC的定時器功能。

評論