基于CPLD的片內環形振蕩器的設計方案

本文介紹一種通用的基于CPLD的片內振蕩器設計方法,它基于環形振蕩器原理,只占用片上普通邏輯資源(LE),無需使用專用邏輯資源(如MaxII中的UFM),從而提高了芯片的資源利用率;振蕩頻率可在一定范圍內調整,振蕩輸出可以驅動內部邏輯和外部器件引腳。本設計有較大的通用性,可方便地在不同CPLD器件間移植,使一些基于CPLD的片上系統(SoC)設計無需使用外部時鐘信號源,從而降低設計成本和難度,增加系統集成度。通過在Altera公司的MAX7000系列EMP7128LC84-15芯片上的實驗說明實現的方法。實驗實現的頻率范圍在8MHz~62MHz。仿真和硬件測試結果表明了該設計方法的正確性和可行性。

1 基于CPLD的片內環形振蕩器

環形振蕩器原理如圖1所示。由奇數個非門組成的環形非門級聯串使電路處于無穩定狀態,靜態下任何一個非門的輸入和輸出都不可能穩定在高電平或低電平,而只能處于周而復始的高低電平轉換狀態,從而產生自激振蕩。振蕩周期為T=2Ntpd,其中N是非門的個數,tpd是每個非門的傳輸延遲時間,改變電路中非門的數量可以改變電路的振蕩頻率。

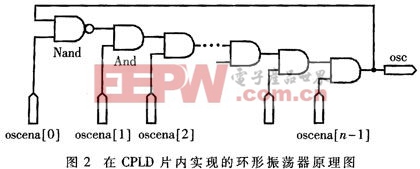

圖1所示的環形振蕩器即使采用電路原理圖輸入,經電子設計自動化(EDA)軟件綜合后,也得不到對應的電路結構。實際上,EDA綜合工具不是從電路結構出發,而是從電路輸入和輸出的邏輯關系出發給出綜合結果,所以,奇數個非門的級聯將被綜合為一個非門,而偶數個非門的級聯被綜合為一個緩沖或一條聯線。為能在CPLD器件中實現圖1的環形振蕩器結構,本文將圖1中單端口輸入元件改成二端口輸入元件,即用二輸入與非門代替圖1的第一個非門,其余偶數個非門則用二輸入與門代替,二端口元件的一個輸入端口連接上級輸出,另一輸入端口作為控制端引出。振蕩器正常工作時控制端全部置高電平。采用Synplify Pro 7.7綜合后的原理圖如圖2所示。該電路完全可實現圖1的功能。

為了保證正反饋,圖1結構的非門級聯必須是奇數個。圖2中的與非門起到反相作用,其他與門則起延時緩沖的作用。可以通過改變門的數量以及選擇門的種類(與門、與非門等)改變osc輸出端的振蕩頻率,而不受"奇數"個門的限制,只要保障第一個門得到正反饋就可以產生振蕩。而圖1的結構必須改變偶數個非門才能達到改變振蕩頻率的目的,因而圖2結構在CPLD芯片中實現時可以節省邏輯資源。控制端oscena[n-1,0]為振蕩使能控制端,置高電平時,與非門的輸入和輸出在緩沖級聯鏈的反饋作用下產生自激振蕩,振蕩器正常工作;控制端的任意一位置零使振蕩器停振。所以oscena既可單獨使用,也可互聯后作為一個端使用。實驗證明,圖2結構能夠保證門延時的等間隔特性。

評論