富士通為28nm SoC器件打造全新設(shè)計(jì)方法

富士通半導(dǎo)體(上海)有限公司日前宣布,成功開發(fā)了專為先進(jìn)的28nmSoC器件量身打造的全新設(shè)計(jì)方法,不僅能實(shí)現(xiàn)更高的電路密度,同時(shí)也可有效縮短開發(fā)時(shí)間。采用全新設(shè)計(jì)方法能夠?qū)㈦娐返拿芏忍岣?3%,并可將最終的線路布局時(shí)間縮短至一個(gè)月。這種設(shè)計(jì)方法將整合至富士通半導(dǎo)體的各種全新定制化SoC設(shè)計(jì)方案中,協(xié)助客戶開發(fā)RTL-HandoffSoC器件。富士通半導(dǎo)體預(yù)計(jì)自2014年2月起將開始接受采用這種全新設(shè)計(jì)方法的SoC訂單。

本文引用地址:http://www.104case.com/article/221249.htm采用28nm等頂尖制程工藝的SoC器件需要有越來越多的功能與效能,進(jìn)而要在芯片中布建越來越多的電路。未來SoC的設(shè)計(jì)將日趨復(fù)雜,開發(fā)時(shí)間也將會(huì)因此較以往增加,同時(shí)如何有效解決功耗問題也成為設(shè)計(jì)者的更大挑戰(zhàn)。

為應(yīng)對日趨復(fù)雜的SoC設(shè)計(jì),富士通半導(dǎo)體所開發(fā)出的創(chuàng)新設(shè)計(jì)方法能實(shí)現(xiàn)更高的電路密度、更短的開發(fā)時(shí)程和降低功耗,并整合至富士通半導(dǎo)體的各種全新定制化SoC設(shè)計(jì)方案中,協(xié)助客戶開發(fā)RTL-HandoffSoC組件。較傳統(tǒng)的設(shè)計(jì)流程,設(shè)計(jì)者可采用富士通半導(dǎo)體的全新設(shè)計(jì)方法在相同大小的芯片中增加33%電路,而且可將最終的線路布局時(shí)間縮短至一個(gè)月。

全新設(shè)計(jì)方法將WhiteSpace有效最小化

全新的獨(dú)家設(shè)計(jì)流程可估算出較容易布線的平面圖,并根據(jù)布線路徑與時(shí)序收斂為內(nèi)部數(shù)據(jù)總線進(jìn)行優(yōu)化。這些設(shè)計(jì)步驟可將無法建置晶體管的WhiteSpace數(shù)量降到最少,因而可讓芯片容納更多電路。

透過專利技術(shù)協(xié)調(diào)邏輯與物理架構(gòu)

此專利技術(shù)無須更動(dòng)任何邏輯設(shè)計(jì),即可自動(dòng)針對物理布線進(jìn)行網(wǎng)表數(shù)據(jù)合成,并可提升整體設(shè)計(jì)的布線效率以及使時(shí)序收斂變得更容易,因而可有效減少最終布線流程所需的時(shí)間,更可達(dá)到更高的密度整合度。

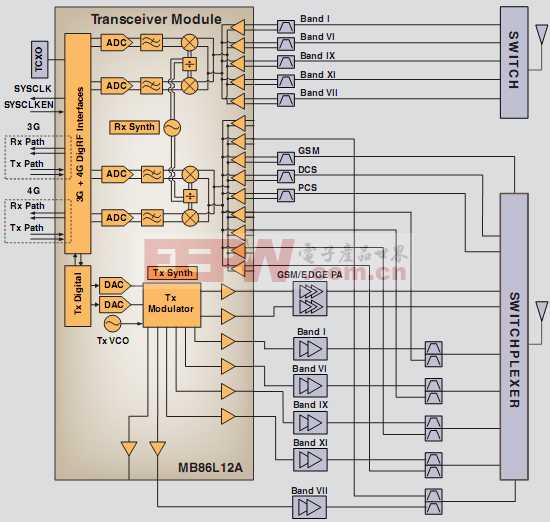

圖1:富士通半導(dǎo)體全新客制化SoC設(shè)計(jì)方法示意圖

富士通半導(dǎo)體是世界級的ASIC供貨商,多年來運(yùn)用在業(yè)界累積的傲人成績和專精技術(shù),持續(xù)提供一站購足的完整定制化SoC解決方案,其中結(jié)合了先進(jìn)設(shè)計(jì)建置、制造服務(wù)和系統(tǒng)級研究、開發(fā)支持等服務(wù)。透過上述解決方案,富士通半導(dǎo)體將能支持客戶快速開發(fā)高效性能及省電的SoC器件。

評論