基于ARM內核SoC的FPGA 驗證環境設計方法

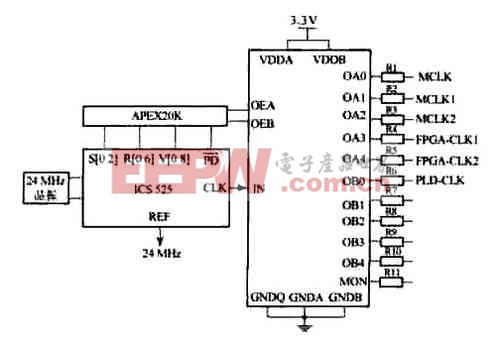

圖3 時鐘電路

時鐘頻率f CLK用下式調節:

式中:f i 為輸入頻率;v 為4~511 中的自然數;r 為0~127 中的自然數;OD 值由S[0 ,1 ,2 ]的3 位決定,S2S1S0的組合為:000 對應十進制10 ,001 對應2 ,010 對應8 ,011 對應4 ,100 對應5 ,101 對應7 ,110 對應9 ,111 對應6。注意:時鐘電路的頻率調節最終通過驅動軟件進行各個參數的配置,在FPGA 內應有相應的配置寄存器,同樣,下面的復位控制模塊也應有復位配置。

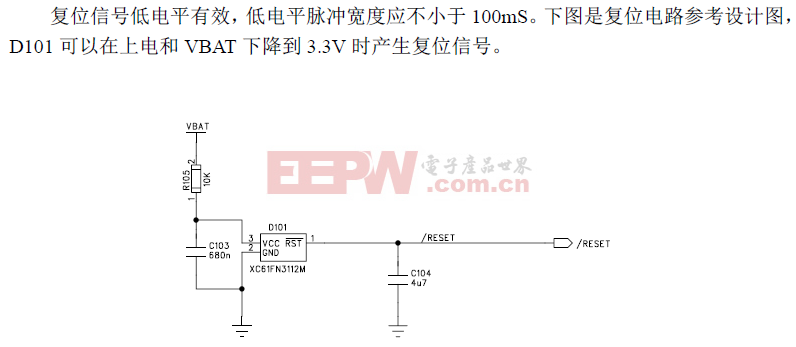

復位電路的設計

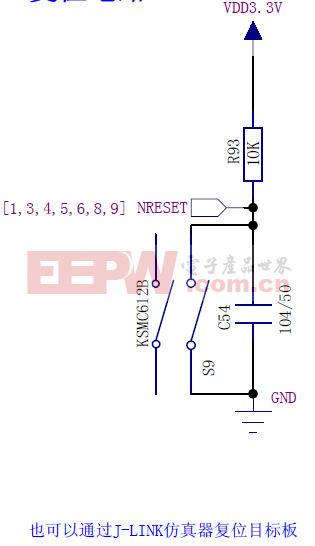

復位信號包括接口模塊中的外部硬件按鍵復位信號reset 、上電復位信號power on reset 、聯合測試訪問專家組(JTAG) 復位信號nTRST 和軟件調試復位信號nSRST。以上幾個信號都是必須的常用復位信號,但ARM7TDMI 核只提供了兩個復位信號接口reset 和nTRST ,為此,以上4 個信號必須加入適當的邏輯電路使其最終形成2 個復位信號,復位信號通路必須滿足復位時序要求且與時鐘信號通路一樣越短越好。

評論