基于ARM內核SoC的FPGA 驗證環境設計方法

摘 要:針對片上系統(SoC) 開發周期較長和現場可編程門陣列(FPGA) 可重用的特點,設計了基于ARM7TDMI 處理器核的SoC 的FPGA 驗證平臺,介紹了怎樣利用該平臺進行軟硬件協同設計、IP核驗證、底層硬件驅動和實時操作系統設計驗證。使用該平臺通過軟硬件協同設計,能夠加快SoC 系統的開發。整個系統原理清晰,結構簡單,擴展靈活、方便。

關鍵詞:SoC;FPGA;軟硬件協同設計;驗證平臺;ARM7TDMI

引 言

隨著片上系統(SoC) 設計的復雜度和性能要求的不斷提高, 軟硬件協同設計(Hardware/ Software Co2de2sign) 貫穿于SoC 設計的始終。軟硬件協同設計是一個以性能和實現成本為尺度的循環優化過程,驗證設計是其中必不可少的重要環節。目前大多數公司提供的開發驗證系統(開發板) 存在兩個弱點:一是開發板的性能、規模難以根據特定的設計需求靈活、自由地調節;二是開發板的功能大多數只能進行軟件代碼的調試,即使ARM公司提供的開發平臺也只能調試部分硬件。這兩個弱點均在一定程度上限制了軟硬件劃分的探索空間,使所設計的SoC 不能獲得更佳結構實現的能力。

本文利用現場可編程門陣列(FPGA) 重用性好、現場靈活性好的優勢,開發一個能進行詳細的行為監測和分析的實時運行驗證平臺,實現軟硬件的緊密和靈活耦合,從而克服上述結構的弱點,以全實時方式運行協同設計所產生的硬件代碼和軟件代碼,構成一個可獨立運行、可現場監測的驗證平臺。這樣,不但能夠提高SoC 流片成功率,加快SoC 的開發,而且可以降低整個SoC 應用系統的開發成本。

驗證平臺的設計

系統設計

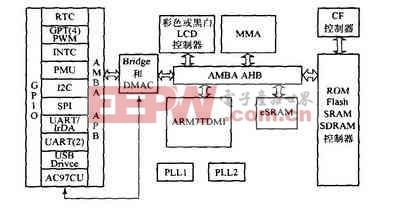

圖1 是我們設計的SoC 系統架構, 選用了ARM7TDMI 處理器核, 它是一個RISC 體系的32 位CPU ,具有功耗低、性價比高、代碼密度高三大特色(ARM公司本身不生產芯片,普通用戶無法獲得ARM可綜合的CPU 核) ,包括AMBA 總線、DMA 控制器和Bridge 、(外部存儲器接口EMI) 、通用串行總線(USB) 客戶端控制器、液晶顯示器(LCD) 控制器、多媒體加速器(MMA) 、AC97 控制器、通用串口/ 紅外(UART/ IrDA) 、通用定時器/ 脈寬調制器(TIMER/ PWM) 、中斷控制器( INTC) 、同步外設接口(SPI) 、實時時鐘(RTC/ WD) 、時鐘和功耗管理單元(PMU) 。

圖1 SoC的系統架構

圖2 是該SoC 驗證平臺的結構框圖,選用Altera公司的APEX20K1500E 作為驗證SoC 用的FPGA ,該器件由一系列的MegaLAB 結構構成,每個結構包含一組邏輯陣列塊(LAB) 、一個嵌入式系統塊( ESB) 及一個在MegaLAB 結構內提供信號通道的MegaLAB 互連。在MegaLAB 結構和I/ O 引腳間的信號布線通過Fast -Track 互連實現。另外,靠邊的LAB 能被I/ O 引腳通過局部互連驅動。

該器件有如下特點:具有多核結構,支持可編程單芯片系統(SOPC) ,密度高,專為低電壓應用設計,最多帶4 個鎖相環的時鐘管理電路,多達8路全局時鐘信號,每個I/ O 引腳具有獨特的三態輸出使能控制及可編程壓擺率控制[1 ,2 ] 。使用該器件作為AMBA 總線模塊、DMA 控制模塊、EMI 模塊、USB 模塊及LCD 控制模塊等多個IP 模塊的硬件載體, 與ARM7 TDMI處理器構成了一個SoC的驗證系統。

評論