龍芯處理器IP核的FPGA驗證平臺設計

本文利用Altera公司的FPGA開發工具對皋于國產龍芯I號處理器IP核的SoC芯片進行ASIC流片前的系統驗證,全實時方式運行協同設計所產生的硬件代碼和軟件代碼,構建一個可獨立運行、可現場監測的驗證平臺。

1、基于龍芯I號處理器IP核SoC芯片

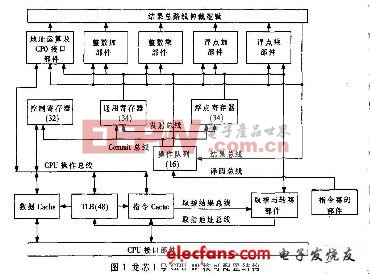

龍芯I號CPU IP核是兼顧通用及嵌人CPU特點的32位處理器內核,采用類MIPS Ⅲ指令集,具有7級流水線、32位整數單元和64位浮點單元;具有高度靈活的可配置性,方便集成的各種標準接口。圖1為龍芯I號CPU IP核可配置結構,用戶可根據自己的需求進行選擇配置,從而定制出最適合用戶應用的處理器結構。

圖1龍芯I號CPU IP核可配置結構

主要的可配置模塊包括:浮點部件、多媒體部件、內存管理、Cache、協處理器接口。浮點部件完全兼容MIPS的浮點指令集合,其相關的系統軟件完全符合ANSI/IEEE 754-1985二進制浮點運算標準。浮點部件主要包括浮點ALU部件和浮點乘法/除法部件,用戶可根據自己的實際應用選擇是否添加。媒體部件復用了MIPS浮點指令的Format域,并復用了浮點寄存器堆,媒體指令集基本對應了Intel SSE媒體指令集合的各種操作。圖2為基于龍芯I號CPU IP核的SoC系統架構。

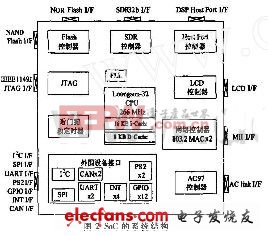

圖2 SoC的系統結構

該SoC芯片支持通用MIPS32指令集,主頻可達266 MHz;內置MAC網絡,提供MII接口;存儲器接口,芯片同時支持SDRAM接口、NOR Flash/ROM和\AND Flash接口,并特置HPI接口可直接與Y0IP CODEC芯片相連;提供豐富的其他外設接凵支持,包括PC接口、UART串口、SP!接口、AC97等接口設備。提供豐富的GP10接口,能夠為“網絡+語音”以及工業控制應用提供高效的單芯片解決方案。

2 FPGA驗證平臺的設計

2.1 FPGA的開發流程

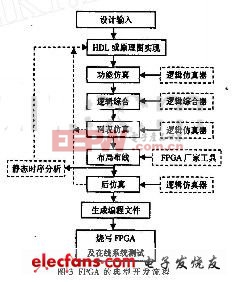

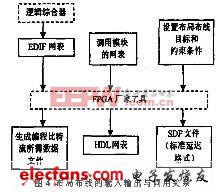

FPGA的典型開發流程如圖3所示。在圖3中,邏輯仿真器主要有Modelsim、Verilog_XL等,邏輯綜合器主要有LeonardoSpectrum、Synplify Pro、FPGA Ex~press/FPGA CompilerII等,FPGA廠家工具有Altera公司的Max+Plusll、Quartusll,Xilinx公司的Foundation ISE、Alliance等。設計輸人主要有原理圖輸人和HDL輸人兩種方式,絕大部分設計,FPGA和ASIC的工程師都使用HDL平臺。設計仿真主要包括功能仿真和網表仿真,設汁仿真需要RTL代碼或綜合后的HDL網表和驗證程序,有時候還需要測試數據,測試數據可能是代碼編譯后的二進制文件或使用專門的工具采集的數據。布局布線工具利用綜合生成的網表、調用模塊的網表,根據布局布線目標,把設計翻譯成原始的目標工藝,最后得到生成編程比特流所需的數據文件。布局布線一般需要的輸人輸出與調用關系如圖4所示。布局布線目標包括所使用的FPGA具體型號等,約束條件包括管腳位置、管腳電平邏輯(LVTIL、LCMOS等)需要達到的時鐘頻率,有時包括部分模塊的布局、塊RAM的位置等。在一般設計中,只需要注意管腳位置和需要達到的時鐘頻率,邏輯端口與FPGA管腳的對應取決于PCB板的設計。

圖3 FPGA的典型開發流程

圖4布局布線的輸入輸出與調用關系

2.2驗證平臺的系統設計

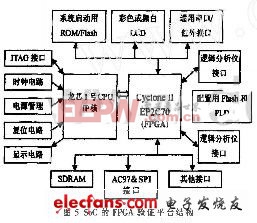

本驗證平臺FPGA采用Altera公司的Cyclone ⅡEP2C70,該器件采用了TSMC領先的90 nm低電介工藝技術生產⒊支持4個可編程鎖相環(PLL),提供靈活的時鐘管理和頻率合成能力;包含了150個18×18 bit乘法器,可以完成基本的DSP處理;高速外接存儲器接口支持SRAM、DRAM\DDR、DDR2以及QDRII SItAM;支持差分和單端I/0標準,包括接收速率805 Mbis和發送速率640 Mb/s的LVDS、mlnl LVDS、LVPECL、 差分HSTL和差分SSTL及處理器、ASSP和ASIC接口的64位66 MHzPCI和PCI-X;高達260 MHz工作頻率,真正的雙端口工作(1個讀和1個寫,2個讀或2個寫);與133 MHz Pal_X1.0標準兼容;用戶最多可用引腳622個;高達402.5 MHz性能的分層時鐘網絡,多達16個全局時鐘線,快速串行配置時間小于100 ms;支持3.3 V、2,5 V或1.8 V多種電壓,可用于視頻、圖像處理(如MPEG4編碼和譯碼、視頻濾波)和無線基礎設各中。基于龍芯I號CPU IP核的SoC的驗證平臺結構如圖5所示。

圖5 SoC的FPGA驗證平臺結構

圖5中,外圍電路的主要功能是驗證SoC中各個接口IP模塊能否與龍芯I號IP核、外部接口單元、硬件驅動軟件和實時操作系統協調高效地工作。由于接口(如USB接口、UART/IrDA接口、SPI和LCD接口等)電路結構比較簡單,且很多資料都有介紹,在設計時,除了注意通用的設計規則和印匍電路板(PCB)布局布線外,沒有特別的要求。同時,為了便于分析各個被驗證的IP模塊在任意時刻的狀態,將Cyclone Ⅱ EP2C70的大多數I/0引腳都引出到PCB上,以方便SoC開發人員使用邏輯分析儀進行信號實時采集和分析,也可讓信號發生器產生一些特定信號以供系統調試使用。該開發系統在設計PCB時還特別注意了電磁干擾的屏蔽問題。

2.3 SoC到FPGA的系統移植

使用Altera公司的FPGA開發工具Quartusll,將SoC向Cyclone Π EP2C70(FPGA)移植的步驟如下

(1)對SoC進行修改,以適合FPGA的開發環境。修改子模塊配置、RAM、FIFO等,添加PLL對所需要的時鐘進行適當的分/倍頻,或提高時鐘信號的質量。

(2)使用Quartusll內置綜合工具或專用綜合工具(如常見的Synplify._pro)單獨建Project,對RTL進行綜合,生成網表。時鐘工作頻率較高的,要寫綜合約束條件。

(3)指定每一個輸人輸出信號對應的FPGA管腳和輸人輸出邏輯類型。

(4)編譯生成的網表以生成sof文件,包括優化、適配、sof文件生成等分步驟。

(5)進行靜態時序分析,檢查是否滿足預定的時鐘頻率要求,若不能滿足,則重新進行第(2)步。如果多次進行步驟(2)仍不能滿足時序要求,則需要根據關鍵路徑對RTL代碼進行修改。

關鍵路徑是指延遲最大的路徑,該路徑的延遲限制了時鐘的最大工作頻率。該SoC芯片的最大工作頻率在266 MHz以上,與選用的FPGA Cyclone Ⅱ EP2C70的總線時鐘速度相當。

3、 VxWorks實時操作系統

本文所設計的SoC硬件平臺上,最終將運行Vx-Works操作系統,作為此次嵌入式SoC硬件平臺設計的軟件需求和最終的驗證目標。VxWorks是一個具有可伸縮、可裁減、高可靠性,同時適用于所有流行CPU平臺的實時操作系統㈣。可伸縮性指VxWorks提供了超過1 800個應用編程接口(API)供用戶自行選擇使用;可裁減性指用戶可以根據自己的應用需要對VxWorks進行配置,產生具有不同功能集的操作系統映像;可靠性指VxWorks可以提供非常安全的操作系統平臺。VxWorks的基本構成組件包括BSP(Board Support Package)、微內核Wind、網絡系統、文件系統及I/0系統。本文測試更關注于BSP、Wind以及I/O組件。BSP中包括硬件環境中CPU的初始化及系統各項硬件資源的安裝和配置,如RAM、Clock、網絡接口、中斷控制器等。微內核Wind是Win ̄dRiver公司自行開發的一種嵌人式操作系統內核,該內核具有標準的嵌人式實時操作系統的基本特征。

4、驗證平臺的檢驗

將已經成熟的AMBA總線IP核的Verilog代碼通過Synplify綜合,利用Altera公司的QUARTUS Ⅱ軟件作布局布線,燒人Cyclone Ⅱ EP2C70,再用同樣的方式將新開發的EMI IP核的Verilog代碼燒入該FPGA,將其中的SDRAM控制器作為驗證示例,選取其中最簡單的訪問方式來驗證該平臺能否使用。上電后,首先要對所有內存區(bank)預充電,經8個自刷新周期后需要設置訪問模式,即編程模式寄存器。以上三個過程要求如下:

(1)預充電命令的發出要求:在時鐘周期的上升沿處,CS、RAS、WE為低,CAS為高。

(2)自刷新命令的發出要求:在時鐘周期的上升沿處,CS、RAS、CAS 禾口CKE保持低,WE為高。

(3)模式寄存器的激活:在時鐘的上升沿處,RAS、CAS、CS和WE為低。

當要驗證各個IP模塊(包括[NT中斷控制器、DMA控制器、LCD控制器和AC97控制器等)之間的協同工作時,燒入的代碼較多,占用的FPGA資源也較多,再加上需要實時運行,例如播放PM3實時解碼過程中,時鐘至少要求60 MHz,需要工作的IP核有總線、DMA控制器、INT中斷控制器、AC97控制器等,因此在這種情況下,最好使用Multi PointSynthesis的綜合流程和Timing driv-en的綜合與優化策略,并使用Logic一lo

評論