基于SoC的實時信號處理系統中存儲系統

數據重組和地址重新生成

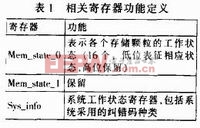

該糾錯容錯邏輯采用了多種方法進行容錯,主要包括采用行冗余模塊實現容錯、降低糾錯能力進行容錯、將用于糾錯的模塊用于容錯等。當自檢模塊發現存儲顆粒出現故障時,將Mem_state寄存器的相應位置為1。而存儲系統的數據組合以及地址生成都是與Mem_state寄存器相關的可配置邏輯。

(1)采用行冗余模塊實現容錯。當自測邏輯發現某個顆粒出現故障時,首先選擇采用行冗余模塊進行容錯的方法。CS片選信號可以看作地址信號的一部分,當寄存器Mem_state中存在一位為1,則出現故障的顆粒所在的存儲顆粒行就會被關閉(拉高CS信號),同時打開冗余行(拉低CS信號),其他信號不變。

(2)將用于糾錯的模塊用于容錯。當自測邏輯發現某個顆粒出現故障且所有的冗余行都已經啟用,可以適當將糾錯的模塊用于容錯。這時需要在地址方面和數據重組方面都進行一定的改動,主要包括:①在故障顆粒所在的行內,故障顆粒的地址和數據都被轉發到空閑顆粒。②所有的數據線依然直接與控制器模塊相連,但在模塊內部,數據重組邏輯自動將冗余顆粒的數據通路重組到故障顆粒的數據通路上來。③糾錯碼編解碼邏輯自動調整編解碼方案。根據相關寄存器的值,糾錯碼的編解碼邏輯自動降低糾錯能力,數據重組邏輯也自動定向糾錯碼的數據通路。圖4為數據重組示意圖。

系統糾錯容錯能力分析

假設各個DDR顆粒之間發生錯誤的概率是互相獨立的,設每個顆粒發生錯誤的概率恒定為λ,則每個DDR顆粒的可靠性符合泊松分布,其可靠性為Rm=e-λt。在Mem(i,j)系統中,每行的可靠性為

整個系統的可靠性為

![]()

重構前后系統可靠性的變化如圖5所示。

由此,可以根據故障概率λ計算出系統的整體可靠性Rsystem,根據系統要求的可靠性可以反向計算出所需要的i,j,從而構建出完整的Mem(i,j)容錯存儲系統。

結論

針對SoC實時數字信號處理系統的特點,設計了一種新的具有自適應容錯糾錯能力的二級冗余存儲體系結構。詳細論述了系統在存儲顆粒組織排列和信號連接方面對于糾錯容錯能力的支持、系統在邏輯設計上對糾錯容錯能力的支持等。新的存儲系統容錯方案可以有效地提高存儲系統的可靠性,下一步的工作將集中在整個系統的低功耗優化方面。

評論