AI芯片的供電挑戰

隨著人工智能 (AI) 工作負載變得越來越大和越來越復雜,為處理所有這些數據而開發的各種處理元素需要前所未有的能力。但是,在不降低信號完整性或引入熱瓶頸的情況下,高效可靠地提供這種電源,已經帶來了半導體歷史上最嚴峻的設計和制造挑戰。

與通用處理器不同,專為 AI 工作負載設計的芯片將密度推向了極端水平。它們將更多的晶體管封裝到更小的封裝中,同時還增加了晶體管的總數,通常以小芯片的形式。結果是更大、更密集的系統級封裝,其中供電不僅僅是一個電氣問題,而且是一個封裝、材料和系統集成挑戰,從單個小芯片延伸到服務器機架。

“功率在很大程度上由動態功率主導,主要由計算和內存之間的數據移動驅動,”Synopsys 研究員 Godwin Maben 說。“例如,NVIDIA 的 Blackwell 功率范圍從 700 瓦到 1,400 瓦不等。這使得高效的總線架構和架構創新(例如數據壓縮策略)變得至關重要。

由于在內存和計算單元之間來回穿梭的數據量很大,因此動態能力占主導地位。這些傳輸使用各種高速互連跨海量內存層次結構進行。但是,移動所有這些數據是有代價的,會產生級聯設計約束,從內存層次結構決策一直延伸到供電網絡 (PDN)。

“當我們轉向背面和 3D 堆疊時,熱量變得更加局部化且更難消散,”imec 研發副總裁 Julien Ryckaert 說。“這種物理壓縮加劇了電遷移和局部熱熱點等挑戰。”

為了在這些級別上易于處理電力傳輸,多學科設計團隊必須全面考慮電壓的調節位置和方式、熱量的提取方式、材料在大電流應力下的行為方式,以及它們在電遷移和 IR 壓降影響可靠性之前有多少裕量。這些設計決策的復雜性要求 EDA 工具、制造工藝和先進封裝之間更加緊密地耦合。

“今天,高性能計算和 AI 加速器已經跨越了千瓦級的界限,”Synopsys 首席架構師 Jay Roy 說。“設計復雜性的爆炸式增長和周期的縮短給半導體 SOC 設計帶來了持續的挑戰。”

這種在最大限度地降低功耗的同時擴展性能的推動迫使電力輸送模式發生重大變化。這不再只是減少阻力。它涉及對具有不同膨脹系數的材料之間的感應行為、熱梯度和耦合進行建模。現在,對電壓降、電流瓶頸和熱熱點的早期預測至關重要,并且必須在實際布局和集成約束的背景下進行。

從橫向到垂直供電

再多的仿真都無法解決傳統橫向供電的固有局限性。在封裝和印刷電路板上橫向布線大電流電源走線會帶來不再擴展的損耗和空間限制。當芯片消耗 100 或 200 瓦時,這種方法是可行的,但現在它已成為現代 AI 硬件的限制因素。

“當前的加速卡通常采用橫向供電架構,從電源模塊到處理器,在幾厘米長的 PCB 走線上路由數千安培的電流,”Saras Micro Devices 首席商務官 Eelco Bergman 說。“由于大電流和走線電阻,這種方法會導致大量的功率損失和過多的熱量產生。此外,可用于支持不斷增長的總功率、電源軌數量以及關鍵高速信號路由的電路板空間是有限的。

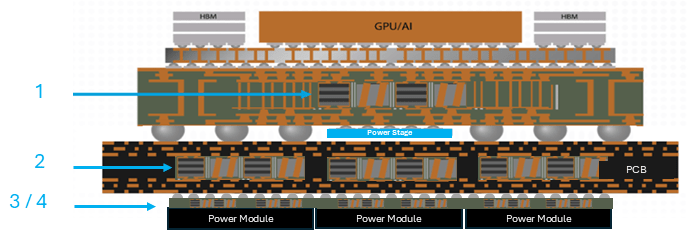

圖 1:垂直供電網絡,顯示直接嵌入封裝基板中的多域電容器模塊。來源:Saras Micro Devices

在這些功率水平下,每一毫歐姆電阻都轉化為必須消散的瓦特熱量。此外,橫向布線施加的空間限制通常會在電源完整性和信號完整性之間造成權衡。在高帶寬系統中,數百個高速 SerDes 通道與密集的電源層共享電路板空間,這些權衡變得站不住腳。

為了克服這些限制,半導體行業越來越多地探索垂直供電。通過將電源軌或穩壓器直接嵌入芯片下方,并用低阻抗路徑垂直連接它們,從源極到硅的距離大大縮小。其結果是減少了 IR 壓降和噪聲,同時為關鍵信號釋放了頂部路由。

Bergman 補充道:“我們看到客戶正在積極探索具有嵌入式電壓調節和集成電容解決方案的垂直供電架構,這些解決方案可以本地化供電。“這些方法釋放了頂部 PCB 空間,減少了寄生損耗,并提高了整體供電性能。”

在襯底和中介層中使用集成的供電層,以及局部去耦,使 AI 小芯片和加速器能夠獲得更清潔、更穩定的功率,同時減少衰減。先進的襯底,包括那些帶有嵌入式無源器件的襯底,現在正在與硅本身共同設計,以優化阻抗曲線和散熱。

同時,這些技術也帶來了新的可靠性挑戰。通過新材料和垂直結構提供大電流需要對電流擁擠、熱循環和材料疲勞進行嚴格的建模。嵌入式功率元件必須能夠承受強熱通量,同時還要與敏感信號層保持電氣隔離。這反過來又推動了介電材料、沉積技術和協同設計方法的創新。

先進的封裝和散熱

高功率密度直接轉化為熱密度,這可能會導致熱點,從而降低可靠性并降低性能。如果沒有先進的熱提取技術,即使是最高效的系統也需要熱節流,這會大大降低性能。

“如今的先進封裝采用多尺度熱管理技術來有效地傳播和去除熱量,”Amkor 小芯片和倒裝芯片球柵陣列 (FCBGA) 業務部高級總監 Gerard John 說。“銦合金 TIM 因其約 80 W/m-K 的高導熱性而特別有效。然而,銦 TIM 需要芯片背面和蓋子底面的金屬化,通常使用 Ti/Au 或 Ni/Au 等材料。回流焊工藝對于在芯片和蓋子之間形成粘合是必要的,這有助于降低界面阻力。

最小化芯片和散熱器之間的熱阻取決于材料和應用技術。均勻的 TIM 覆蓋率和低空隙率加工對于實現整個芯片的一致散熱至關重要。傳統的基于焊料的 TIM 正在被高性能金屬合金、相變材料和新型碳基界面所取代或補充。

“確保 TIM 應用中的最小空隙至關重要,”John 說。“空隙會嚴重阻礙導熱性,導致熱點和器件可靠性降低。監測 TIM 空隙對于工藝優化和設備篩選至關重要。

這些解決方案通常是針對特定工作負載量身定制的。例如,AI 訓練產生的持續功率爆發比推理更長,并且需要不同的熱瞬態響應。包裝工程師必須與系統架構師合作,以確保冷卻解決方案與實際作配置文件相匹配。

“TIM 的選擇通常基于設備功率圖,這些圖顯示了高熱量產生區域,”John 指出。“通過將 TIM 屬性與這些映射相匹配,可以實現最佳熱管理,確保整個器件的高效散熱。”

在多芯片系統中,熱邏輯模塊的接近會放大熱挑戰。先進的設計正在轉向均溫板、微流體冷卻和雙面熱提取來管理這種復雜性。每種方法都引入了新的制造、可靠性和材料集成障礙,但它們正迅速成為大規模實現 AI 性能的重要工具。

鉬和材料遷移

隨著 AI 加速器需要更大的功率和更緊密的集成,傳統的前端材料正在顯現其老化。鎢和銅廣泛用于局部互連和觸點一直是其導電性和可制造性的行業標準,但現在它對芯片最致密的部分施加了限制。

這就是鉬成為關鍵替代金屬的地方。鉬的電子平均自由程比銅短,在狹窄幾何形狀中的可擴展性比鎢好,在先進節點的電阻率和可制造性方面都有了明顯的改善。

“從傳統的鎢金屬化過渡到鉬提供了實質性的性能改進,包括將接觸電阻降低多達 50%,”Lam Research 公司副總裁兼總經理 Kaihan Ashtiani 說。“鉬的電子平均自由程較短,使其更適合更小的尺寸,顯著減少了緊密排列的互連結構中的電阻問題。”

這在實踐中意味著鉬在局部互連中變得特別有利,其中線寬和間距現在低于 20nm。在這些尺寸下,鎢等傳統金屬的電子散射增加,從而導致更高的有效電阻率和熱負荷。相比之下,鉬在受限幾何形狀中保持良好的導電行為。

對于 AI 設備,此屬性至關重要。隨著更多的功能被封裝在更小的平方毫米中,以及垂直堆疊變得越來越普遍,熱量和電阻越來越局限。鉬等材料創新通過提高電氣性能并簡化與原子層沉積 (ALD) 和化學氣相沉積 (CVD) 工藝的集成,幫助減輕這些影響,這些工藝在尖端晶圓廠中已經很常見。

“當互連尺寸縮小到銅等金屬的平均自由程以下時,由于電子散射更頻繁,電阻會增加,”Ashtiani 說。“在這些情況下,像鉬這樣的金屬,具有較短的平均自由程,實際上變得更有利,因為它在較小的尺度上保持較低的電阻。”

向鉬的轉變也與更廣泛的行業努力降低電遷移風險相一致。在 AI 工作負載中常見的高電流密度下,金屬遷移會隨著時間的推移產生空隙和開路,這是對可靠性的日益關注的問題。鉬的高熔點和晶粒穩定性有助于抵消這一點,使其成為長壽命 AI 計算應用的有力候選者。

雖然尚未普及,但鉬的采用正在加速,尤其是在 GPU 矩陣引擎和 SRAM 陣列等功率密度極高的應用中。它還在包含背面供電的設備中越來越受歡迎,其中金屬化層的復雜性需要高度保形和低電阻率的材料。

背面供電

也許當今芯片架構最具變革性的轉變是轉向背面供電網絡 (BSPDN)。BSPDN 不是通過爭奪空間的頂部金屬層來路由電源和信號,而是通過在晶圓的底部引入電源連接來解耦這些功能。

最初的概念最初由 Intel 宣傳為“Power vias”,此后演變為整個行業采用的更廣泛的技術類別。從本質上講,晶圓的背面被蝕刻以露出觸點,然后用于直接向晶體管供電,繞過信號路由堆棧并顯著提高效率。

“背面供電始于將電源過孔蝕刻到硅中,以提供從背面直接供電,這有助于降低阻抗,”imec 的 Ryck?ert 說。“從兩側處理晶圓為器件擴展和布線密度開辟了新的機會,盡管由于去除了作為散熱器的硅,它也帶來了熱挑戰。”

這種結構重組為 AI 芯片提供了幾個關鍵優勢。首先,通過分離電源和信號布線,工程師在布局規劃和時序優化方面獲得了更大的靈活性。信號層可以擴展或微調,而無需擔心功率分配限制。其次,它使電網更薄、更均勻,從而減少了 IR 壓降,使電壓調節更具可預測性。

“電力輸送曾經是眾多考慮因素之一,”Ryckaert 補充道。“現在它塑造了整個平面圖。背面 PDN 有助于緩解布線擁堵并實現更高的晶體管密度,但它們也增加了功率密度,這使得熱管理比以往任何時候都更加重要。

此外,背面加工引入了新的冷卻選項。由于硅襯底不再是散熱的屏障,因此設計人員可以實施雙面冷卻策略,其中熱界面應用于芯片的兩側。

然而,反向供電并非沒有挑戰。它需要全新的工藝流程和材料進步,包括晶圓減薄、硅通孔 (TSV) 對準、混合鍵合和處理極其脆弱的芯片。這些結構的機械可靠性仍在研究中,產量優化仍然是大批量采用的障礙。

設計協同優化和系統級影響

盡管背板電源、鉬互連和垂直 PDN 的技術前景廣闊,但這些進步都不是孤立發生的。下一代 AI 芯片將需要在整個設計堆棧中采用更緊密集成的方法,使用通常所說的系統技術協同優化 (STCO)。

在此模型中,芯片架構師、封裝工程師和系統設計人員從最早的設計階段開始協作。輸電網絡、熱分布、機械應力和平面圖必須建模為相互依賴的系統,而不是流程中的連續步驟。

“功耗感知協同設計越來越重要,”Synopsys 的 Maben 說。“它有助于平衡熱性能與時序收斂,使客戶能夠在最終產品中實現更高的效率和可靠性。”

在系統級別,這些優化具有廣泛的后果。例如,熱節流是 AI 芯片性能面臨的最大威脅之一。如果沒有對局部加熱進行有效預測和緩解,否則設計良好的系統在現場可能會表現不佳。

“上游輸電效率的邊際提高可以防止下游的熱降解,”Synopsys 的 Roy 說。“目標是讓工程師及早了解這些系統如何交互,以便可靠性是內置的,而不是附加的。”

這的影響遠遠超出了模具。系統集成商必須考慮整個堆棧(芯片、中介層、基板和 PCB)的 PDN 阻抗。信號完整性、板級去耦和外殼級氣流都會影響高能效芯片在實際應用中是否按預期運行。

這些約束提高了協同仿真和跨域反饋循環的重要性。電壓完整性和電磁干擾 (EMI) 現在與熱仿真、材料建模和功耗感知驗證直接交叉。作為回應,一些芯片制造商正在將封裝和系統工程團隊引入內部,或將他們嵌入芯片設計團隊,以加快迭代并確保一致性。

除了技術協調之外,經濟激勵還推動了協同優化。通過添加多余的電容、更寬的電源層或過度設計的 VRM 來過度配置供電系統會消耗電路板面積和資源,否則這些資源可能會用于計算。

“減少 IR 壓降和提高輸電效率直接轉化為更少的熱量和更低的冷卻成本,”Saras 的 Bergman 說。“這是超大規模數據中心的直接成本優勢。”

結論

隨著 AI 需求的增長,優化每一瓦特和交付它所花費的每一美元的壓力只會越來越大。這意味著電力輸送不再是后端考慮因素。它已成為塑造 AI 芯片設計和制造方式的一線約束。隨著 AI 芯片進入千瓦級市場,該行業必須重新考慮從材料到平面圖、晶圓鍵合到散熱的方方面面。背面供電網絡、鉬互連和垂直集成基板等創新只是一個開始。

AI 芯片的供電之路需要跨學科的深度合作。隨著工程師面對下一代電力輸送的多物理場性質,圍繞硅、封裝和系統設計構建的孤島正在瓦解。雖然這些解決方案的成本和復雜性很高,但以性能、效率和可擴展性衡量的回報將是巨大的。

評論