如何通過(guò)混合信號(hào)仿真優(yōu)化硅光子學(xué)

Silicon photonics 正在重塑數(shù)據(jù)中心的未來(lái)。但工程師需要更先進(jìn)的仿真工具來(lái)將這些輕型吊索組件與電子設(shè)備集成。

本文引用地址:http://www.104case.com/article/202506/471472.htm當(dāng)今的計(jì)算和通信應(yīng)用程序需要前所未有的處理能力和高帶寬內(nèi)存訪問(wèn)。以光速傳輸?shù)臄?shù)據(jù)正在成為解決方案。

在數(shù)據(jù)中心,GPU 通常在 AI 訓(xùn)練和推理期間每秒相互傳輸數(shù) TB 的數(shù)據(jù),遠(yuǎn)遠(yuǎn)超過(guò)了傳統(tǒng)銅纜互連的限制,后者的最高速度為每秒數(shù)百兆比特。光互連已成為滿足這些需求的解決方案,它使用光束以高達(dá) 100 Gb/s 的速度傳輸數(shù)據(jù)。但是,設(shè)計(jì)和驗(yàn)證此類復(fù)雜系統(tǒng)需要高級(jí)仿真工具來(lái)對(duì)其性能進(jìn)行建模,并確保組件的無(wú)縫集成。

光連接的未來(lái)完全與硅光子學(xué)有關(guān)。該技術(shù)將光學(xué)和電子元件合并到單個(gè)硅芯片中,從而實(shí)現(xiàn)高效和高帶寬的數(shù)據(jù)移動(dòng)。它在數(shù)據(jù)中心互連、5G 無(wú)線網(wǎng)絡(luò)、城域網(wǎng)和長(zhǎng)途電信、高性能計(jì)算 (HPC) 和 AI 等領(lǐng)域變得越來(lái)越普遍。它還有可能在量子計(jì)算中發(fā)揮作用。

如今,這些系統(tǒng)包含復(fù)雜的模擬和數(shù)字組件網(wǎng)絡(luò)。但是,將硅光子學(xué)集成到這些混合信號(hào)系統(tǒng)中,會(huì)給芯片設(shè)計(jì)人員和系統(tǒng)工程師帶來(lái)更多的復(fù)雜性。對(duì)電氣、光學(xué)和數(shù)字域執(zhí)行精確仿真的能力對(duì)于開(kāi)發(fā) AI 工作負(fù)載和其他應(yīng)用程序所需的高帶寬、低延遲連接至關(guān)重要。

硅光子學(xué)的構(gòu)建模塊

從根本上說(shuō),硅光子學(xué)就是將光速帶入 CMOS 世界。

通過(guò)將激光器、波導(dǎo)和光電探測(cè)器等組件集成到單個(gè)基板上,這些系統(tǒng)可以精確控制光線。激光器和發(fā)光二極管 (LED) 等光源將電信號(hào)編碼為可見(jiàn)光或紅外光,將電子轉(zhuǎn)換為光子。相比之下,光電二極管和其他光探測(cè)器執(zhí)行相反的過(guò)程,將透射的光轉(zhuǎn)換為電信號(hào)。

光波導(dǎo)充當(dāng)光的管道,類似于銅線傳輸電信號(hào)的方式。雖然激光器在集成到系統(tǒng)之前是單獨(dú)制造的,但波導(dǎo)往往直接放置在硅芯片上。在許多情況下,這些波導(dǎo)可以進(jìn)行電氣控制,從而能夠動(dòng)態(tài)控制其折射率,以調(diào)整透射光的相位和強(qiáng)度。因此,這些組件可用于過(guò)濾或調(diào)制光束。

光耦合器和分路器進(jìn)一步增強(qiáng)了系統(tǒng)功能。合路器合并來(lái)自多個(gè)來(lái)源的信號(hào),允許基于干擾的調(diào)制,而分路器將光信號(hào)分成幾個(gè)不同的輸出,功率分配成比例。這些組件構(gòu)成了硅光子學(xué)的構(gòu)建塊,對(duì)于數(shù)據(jù)中心的波分復(fù)用 (WDM) 等應(yīng)用至關(guān)重要。

Silicon Photonics:從服務(wù)器內(nèi)部到 SoC 內(nèi)部

硅光子系統(tǒng)以各種配置部署,從安裝在 PCI Express (PCIe) 卡上或直接安裝在主板上的獨(dú)立設(shè)備到通過(guò)光學(xué)背板連接的整個(gè)服務(wù)器機(jī)架。

但最新的創(chuàng)新之一是將光學(xué)小芯片集成到多晶粒系統(tǒng)中。這些封裝的核心是系統(tǒng)級(jí)芯片 (SoC),主要是數(shù)字式的,通常包含數(shù)百億個(gè)晶體管。它們充當(dāng)服務(wù)器或網(wǎng)絡(luò)交換機(jī)的主處理單元,使用電氣 I/O 與系統(tǒng)中的其他芯片(或者,在交換機(jī)的情況下,與可插拔光學(xué)器件的端口)通信。然而,半導(dǎo)體公司的目標(biāo)是將硅光子收發(fā)器小芯片集成到同一封裝中,以克服電氣 I/O 的限制。

在基于小芯片的光互連領(lǐng)域,Intel 最近推出了一種新的 OCI 兼容光小芯片,通過(guò)單模光纖提供 64 個(gè)雙向通道和高達(dá) 4 Tb/s 的吞吐量。IBM 的共封裝光學(xué)模塊直接與主機(jī)芯片集成,將海濱光纖密度提高了六倍。

硅光子學(xué)小芯片用作高速光收發(fā)器。它們通過(guò)光纖而不是銅線在同一服務(wù)器、同一機(jī)架甚至不同機(jī)架中的芯片之間移動(dòng)數(shù)據(jù)。這些架構(gòu)表明,對(duì)結(jié)合模擬、數(shù)字和光域的異構(gòu)系統(tǒng)的精確仿真的需求日益增長(zhǎng)。

共封裝光學(xué)器件的挑戰(zhàn)在于,硅光子學(xué)小芯片集成了光學(xué)和電子元件,從而創(chuàng)建復(fù)雜的混合信號(hào)系統(tǒng),需要嚴(yán)格的仿真和驗(yàn)證才能確保最佳性能。此外,芯片設(shè)計(jì)人員和系統(tǒng)工程師還必須考慮廣泛的其他因素,從散熱和功率效率到信號(hào) (SI) 和電源完整性 (PI)。

這些架構(gòu)需要改變系統(tǒng)級(jí)交互的建模和驗(yàn)證方式。隨著光學(xué)元件越來(lái)越接近處理內(nèi)核,邏輯仿真必須不斷發(fā)展,以捕獲不同時(shí)間尺度和抽象級(jí)別的電光交互。

例如,光互連與射頻前端的集成(就像最新的異構(gòu)硅光子接收器設(shè)計(jì)一樣)強(qiáng)調(diào)了對(duì)精確行為和布局感知建模的需求。異構(gòu)光子 IC 的總結(jié)進(jìn)一步強(qiáng)調(diào)了跨光學(xué)、模擬和數(shù)字域的協(xié)同仿真的作用。

這些發(fā)展加強(qiáng)了可擴(kuò)展的混合信號(hào)仿真和建模框架的重要性,這些框架可以在功能、物理實(shí)現(xiàn)和系統(tǒng)性能之間架起橋梁。

模擬多晶片硅光子系統(tǒng)的挑戰(zhàn)

然而,設(shè)計(jì)具有集成硅光子元件的多晶粒系統(tǒng)面臨著獨(dú)特的挑戰(zhàn)。

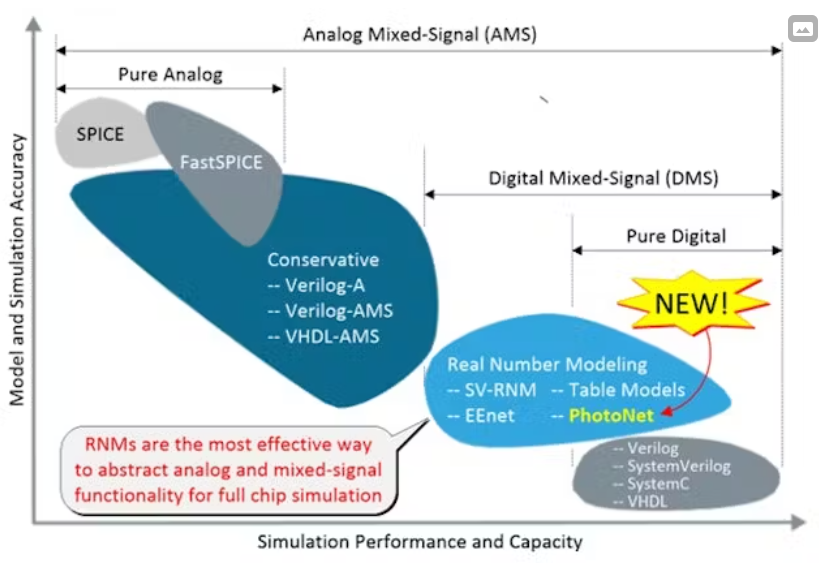

半導(dǎo)體供應(yīng)商通常為支持硅光子學(xué)的特定工藝節(jié)點(diǎn)提供工藝開(kāi)發(fā)套件 (PDK),其中包含電子和光學(xué)元件的精確模型。在大多數(shù)情況下,這些模型采用嚴(yán)格的模擬格式,例如 SPICE 或 FastSPICE,或采用硬件描述語(yǔ)言 (HDL),例如 Verilog-A、Verilog-AMS 或 VHDL-AMS,所有這些都可用于模擬仿真。這些模型在模擬域中為您提供高精度和相對(duì)較快的性能。

然而,使用模擬仿真工具進(jìn)行混合信號(hào)驗(yàn)證(也稱為模擬混合信號(hào) (AMS))可能會(huì)導(dǎo)致仿真速度非常慢且耗費(fèi)資源。光子系統(tǒng)的復(fù)雜性加劇了這些挑戰(zhàn),需要新的方法來(lái)確保精度和效率。

即使在相對(duì)簡(jiǎn)單的 implementations 中,設(shè)計(jì)和驗(yàn)證過(guò)程也可能很復(fù)雜。例如,使用不同波長(zhǎng)的多個(gè)不同光源的發(fā)射機(jī)小芯片必須確保光纖另一端的接收機(jī)小芯片能夠準(zhǔn)確分離和處理這些信號(hào)。系統(tǒng)必須驗(yàn)證光波導(dǎo)和調(diào)制器在各種電壓條件下是否有效工作。當(dāng) chiplet 被設(shè)計(jì)為充當(dāng)收發(fā)器時(shí),復(fù)雜性會(huì)顯著增加。

實(shí)數(shù)建模:混合信號(hào)仿真的下一階段

實(shí)數(shù)建模 (RNM) 是彌合模擬域和數(shù)字域之間差距的一種方法(見(jiàn)圖)。

Cadence 設(shè)計(jì)系統(tǒng)![]() 混合信號(hào)仿真的模型和仿真精度與性能和容量的關(guān)系。

混合信號(hào)仿真的模型和仿真精度與性能和容量的關(guān)系。

這些模型使工程師能夠使用數(shù)字工具仿真模擬行為,從而顯著提高仿真速度和容量。最重要的一點(diǎn)是,這些模型都是基于 SystemVerilog 的。因此,RNM 模型可用于在統(tǒng)一的仿真環(huán)境中驗(yàn)證和確認(rèn)模擬、數(shù)字和光學(xué)組件。

通過(guò)簡(jiǎn)化仿真過(guò)程,RMN 幫助工程師以更高的速度和可靠性驗(yàn)證復(fù)雜的混合信號(hào)系統(tǒng)。

當(dāng)在 SPICE 或 Verilog-A 中創(chuàng)建的模擬模型不足以應(yīng)對(duì)需要集成光子元件、模擬電路和數(shù)字控制器的混合信號(hào)仿真時(shí),RNM 特別有價(jià)值。通過(guò)在數(shù)字驗(yàn)證工作流程中實(shí)現(xiàn)高速仿真,RNM 有助于消除與傳統(tǒng)模擬和數(shù)字混合信號(hào)協(xié)同仿真相關(guān)的瓶頸。

EDA 在硅光子學(xué)中不斷發(fā)展的作用

EDA 公司一直在推出一類新型數(shù)字混合信號(hào) (DMS) 仿真工具,以幫助降低集成光學(xué)元件和電子元件的復(fù)雜性。

例如,Cadence Xcelium 數(shù)字仿真器完全支持 RNM,支持集成光子域和電域的混合信號(hào)仿真。它的與眾不同之處在于速度 — DMS 模擬的運(yùn)行速度明顯快于傳統(tǒng)的 AMS 模擬。同時(shí),它保持了對(duì)整個(gè)多晶粒系統(tǒng)進(jìn)行建模的能力。

Cadence 還開(kāi)發(fā)了一個(gè)名為 PhotoNet 的庫(kù),使工程師能夠訪問(wèn)參數(shù)化的 RNM,其中包括最常見(jiàn)的硅光子元件,例如激光器、探測(cè)器、波導(dǎo)、合路器和分路器。新庫(kù)可以與該公司的 EENet 庫(kù)一起使用,該庫(kù)包含參數(shù)化的 RNM 模型,代表電阻器、電感器和電容器器件,以及二極管、晶體管、運(yùn)算放大器和其他模擬功能。

使用 PhotoNet,工程師可以仿真硅光子學(xué)的功能,并驗(yàn)證其與數(shù)字控制器和模擬組件的集成。PhotoNet 模型允許工程師驗(yàn)證光波導(dǎo)和調(diào)制器在特定電壓條件下是否按預(yù)期工作。與 EENet 相結(jié)合,這種方法可以更有效地驗(yàn)證混合信號(hào)多晶粒系統(tǒng),減少設(shè)計(jì)迭代并加快上市時(shí)間。

Cadence 還推出了快速采用工具包 (RAK),提供參考代碼,向工程師展示如何在同一系統(tǒng)中對(duì)電氣、光學(xué)和數(shù)字組件進(jìn)行建模,然后驗(yàn)證所有組件是否協(xié)同工作。

這些工具在克服設(shè)計(jì)和驗(yàn)證包含硅光子元件的多晶粒系統(tǒng)的挑戰(zhàn)方面發(fā)揮著關(guān)鍵作用。DMS 可以通過(guò)在電氣、光學(xué)和數(shù)字域中實(shí)現(xiàn)精確建模,幫助驗(yàn)證和確認(rèn)未來(lái)應(yīng)用所需的高帶寬系統(tǒng)。因此,工程師可以自信地設(shè)計(jì)和驗(yàn)證下一代高性能系統(tǒng),滿足數(shù)據(jù)中心、電信、HPC 和 AI 等市場(chǎng)不斷變化的需求。

賭注只會(huì)越來(lái)越高。新的架構(gòu)方法有望將硅光子學(xué)推向新的計(jì)算角色。例如,研究人員開(kāi)發(fā)了一種完全集成的光子張量核心,突出了片上光學(xué)矩陣作的潛力。隨著硅光子學(xué)越來(lái)越多地與數(shù)字邏輯協(xié)同設(shè)計(jì),DMS 和其他協(xié)同仿真工具可能至關(guān)重要,使工程師能夠在制造芯片之前仿真信號(hào)在電氣、光學(xué)和數(shù)字域中的行為。

評(píng)論