先進封裝:TSMC在FOPLP和CoPoS方面的戰(zhàn)略推動

先進封裝被廣泛認為是擴展和超越摩爾定律的關(guān)鍵技術(shù)途徑。面對芯片擴展的物理限制和工藝節(jié)點小型化步伐的放緩,先進封裝通過系統(tǒng)級封裝 (SiP)、異構(gòu)集成和高密度互連實現(xiàn)計算性能和能效的持續(xù)改進。

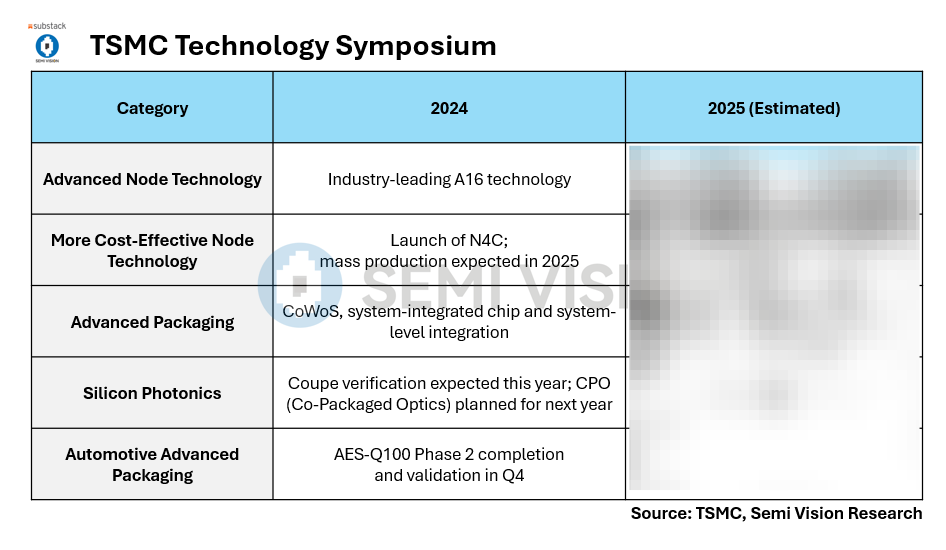

本文引用地址:http://www.104case.com/article/202504/469942.htm臺積電的技術(shù)論壇即將舉行,據(jù)外媒報道,預計臺積電將在活動中討論 CoPoS 的技術(shù)概念。這將與 2025 Touch Taiwan 技術(shù)論壇同時進行,產(chǎn)生協(xié)同效應。SemiVision Research 將對 CoPoS 技術(shù)進行深入討論,并分析臺灣和全球供應鏈格局。

由于這種封裝技術(shù)與基于面板的工藝密切相關(guān),臺灣面板制造商群創(chuàng)光電已成為討論中的領先公司。然而,他們的主要關(guān)注點一直是 FOPLP(扇出面板級封裝)而不是 CoPoS。

FOPLP(扇出面板級封裝)和 CoPoS(Chip-on-Panel-on-Substrate)都使用大型面板基板進行封裝,但它們在架構(gòu)和應用方面存在顯著差異,尤其是在中介層的使用方面。FOPLP 是一種沒有中介層的封裝方法,其中芯片芯片直接重新分配到面板基板上,并通過再分配層 (RDL) 互連。這帶來了成本更低、I/O 密度高和外形尺寸靈活的等優(yōu)勢,使其適用于集成密度適中的邊緣 AI、移動設備和中端 ASIC 等應用。

相比之下,CoPoS 集成了中介層,可實現(xiàn)更高的信號完整性和穩(wěn)定的功率傳輸,這在集成多個高性能、高功率芯片(如 GPU 和 HBM)時尤為重要。中介層的存在使 CoPoS 更適合需要大面積封裝和高速數(shù)據(jù)傳輸?shù)母叨?AI 和 HPC 系統(tǒng)。

此外,CoPoS 中的中介層材料正在從傳統(tǒng)的硅發(fā)展為玻璃,這提供了更好的成本效益和熱穩(wěn)定性。玻璃中介層還提供改進的熱膨脹系數(shù) (CTE) 匹配和減少翹曲,從而提高產(chǎn)量和更好的大面積集成工藝控制。這是臺積電及其供應鏈合作伙伴的重點,將 CoPoS 定位為未來 CoWoS-L 的潛在替代品。

之前,我們深入討論了為什么先進封裝是必不可少的,并分析了臺積電對 Chip-on-Panel-on-Substrate (CoPoS) 的戰(zhàn)略推廣。這種方法響應了不斷增長的 AI GPU 封裝面積需求和 CoWoS 的產(chǎn)能限制,基于面板的基板成為未來擴展和成本優(yōu)化的關(guān)鍵推動因素。

現(xiàn)在,我們將重點轉(zhuǎn)向TSMC在扇出面板級封裝 (FOPLP) 和更廣泛的 CoPoS 生態(tài)系統(tǒng)方面的現(xiàn)狀。

新興的 FOPLP 和 CoPoS 技術(shù)推動測試和分析行業(yè)

由于人工智能技術(shù)需要更快的處理速度和更低的功耗,臺積電 一直在積極投資先進封裝和硅光子學。這一戰(zhàn)略舉措刺激了測試和分析領域的需求增加,行業(yè)專家樂觀地認為,CoPoS、FOPLP(扇出面板級封裝)和硅光子學等發(fā)展將繼續(xù)推動這一需求,從而加強 HKC、愛德萬測試和宜特等測試公司的運營。

CoPoS 是一種簡化從晶圓到面板形式的過渡的技術(shù),類似于 CoWoS 的面板化,并利用方形基板來集成更多芯片,從而提高生產(chǎn)效率和成本效益。但是,高溫翹曲問題需要通過廣泛的測試和分析來解決。

此外,據(jù)報道,臺積電的第一代硅光子學產(chǎn)品,緊湊型通用光子引擎 (COUPE) 已進入驗證階段,并計劃與共封裝光學器件 (CPO) 模塊一起進一步開發(fā)。這些技術(shù)需要額外的測試來支持最初的行業(yè)增長階段。

愛德萬測試最近在中國臺灣和日本獲得了硅光子光損耗檢測設備的專利。這些器件可以識別半導體光導芯片路徑中的異常情況,例如衰減、泄漏和斷開,為解決光子集成電路 (PIC) 中普遍存在的問題鋪平了道路,并利用了硅光子學市場的潛力。

愛德萬測試去年的巨額資本支出最初抑制了利潤,但對今年硅光子學和先進工藝技術(shù)收獲階段的預期表明運營和盈利能力有所改善。

宜特持續(xù)強化核心技術(shù)與客戶服務,聚焦五大關(guān)鍵領域的先進制程與包裝。這包括強調(diào) CPO、TGV(穿玻璃通孔襯底)和 TSV(通硅通孔)解決方案,預計今年的收入和利潤將出現(xiàn)雙增長。

香港通訊還努力培育先進的流程,對中國臺灣和日本市場的穩(wěn)定增長前景持樂觀態(tài)度。隨著他們最近在今年第一季度的北海道實驗室落成,材料分析業(yè)務連續(xù)性和產(chǎn)品組合優(yōu)化應該會提高未來的盈利能力。

關(guān)鍵見解表

| 方面 | 描述 |

|---|---|

| CoPoS 技術(shù) | 提高了芯片集成度和效率,但由于翹曲問題需要測試。 |

| 硅光子學 | 臺積電正在開發(fā)的開創(chuàng)性 COUPE 產(chǎn)品,促進行業(yè)合作。 |

評論