50%新型HPC采用多芯片設計

一直以來,芯片制造商都是通過轉向更小的工藝節點來實現功耗/性能、功能、外形尺寸和成本目標。然而,因為需要不斷提高處理能力,導致 SoC 的尺寸變得極大——無法在保證合理良率的前提下制造這些產品。這代表市場正式進入了無法僅憑轉移到高級節點便可滿足目標的階段。

本文引用地址:http://www.104case.com/article/202503/467518.htm隨著裸晶尺寸接近制造設備的極限點位,將滿足計算密集型應用所需的所有邏輯、IO 和內存全部封裝到一塊物理芯片上變得不再經濟實惠。因此,芯片設計人員將芯片設計拆分為多個尺寸更小、更容易制造、良率也更高的裸晶。

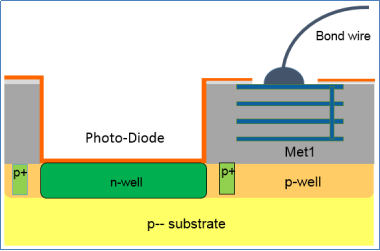

簡而言之,多裸晶設計是將大型設計拆分為多個通常被稱為芯粒或晶片的小尺寸裸晶,并將其集成到單個封裝中,以獲得預期的功耗和外形尺寸目標。單片設計是將所有的功能封裝到一個硅片上,而多裸晶方法則能夠提供產品模塊化和靈活性,允許通過混合封裝不同的裸晶來滿足不同的細分市場或需求。

例如,面向低端、中端和高端等各級細分市場的終端產品均可受益于多裸晶方法。多裸晶設計在混用工藝節點方面也具有靈活性。例如,著重計算功能的處理器可位于高級節點上,而著重 IO 功能的處理器則可位于傳統節點上,從而確保二者都能最高效地利用技術節點。

多裸晶設計架構可以采用不同的格式。裸晶可以并排放置,并通過專用 die-to-die 接口相連接,這是一種普遍且成本較低的方法。如想獲得更高的密度,可以將這些組塊封裝在 2.5D 或 3D 設計中。集成了的 GPU 和高帶寬內存 (HBM)2.5D 設計在中介層中封裝了 4 到 12 個大型 HBM,是這十年來的人工智能的主力軍。隨著時代的進步,2.5D 設計目前正在設法進軍 5G 基礎設施、數據中心和大型網絡系統等新終端市場。

到目前為止,多芯片技術、工具、流程和 IP 已經迅速成熟。工程專業知識不斷發展。代工廠產能不斷擴大。考慮到這一點,研究機構預測 2025 年 50% 的新 HPC 芯片設計將采用 2.5D 或 3D 多芯片。

代工廠正在為 2.5D 和 3D 多芯片設計浪潮做準備

將 2.5D 和 3D 多芯片設計推向市場需要的不僅僅是研發,還需要高帶寬、低延遲互連 (3DIO)、具有足夠產能的先進制造工藝以及精密的設計工具和 IP。

UCIe(通用芯片互連標準)等開放行業標準日趨成熟,有助于簡化和加強異構芯片之間的連接,同時降低風險并縮短設計周期。UCIe 在 HPC、AI、數據中心和邊緣應用中的采用日益廣泛,推動了對 2.5D 和 3D 多芯片設計的巨大需求。

除了先進互連技術的成熟和普及之外,代工廠還在為即將到來的 2.5D 和 3D 多芯片設計浪潮做準備。這包括提供更密集凸塊和更高性能的新制造工藝。附加封裝、中介層和集成選項提供了成本和架構靈活性。而擴大生產能力意味著可以將更多設計和原型推向市場。

先進的多芯片設計工具和 IP

如果沒有最先進的設計解決方案,就不可能開發這些尖端芯片。Synopsys 全面且可擴展的多芯片解決方案(包括設計自動化工具和 IP)可實現:

早期架構探索。

快速軟件開發和系統驗證。

高效的芯片/封裝協同設計。

強大的芯片間和芯片間連接。

改進制造工藝和可靠性。

具體來說,如今的 3DIC Compiler 是一個統一的探索到簽核平臺,適用于 2.5D 和 3D 多芯片設計。它已獲得所有主要代工廠的認證,支持可行性探索、多芯片分區以及用于原型設計和布局規劃的代工廠技術選擇。這支持分析驅動的設計實施(包括高級封裝和芯片到芯片布線)和黃金簽核驗證。

3DIC Compiler 還與 AI 驅動系統分析和優化解決方案 3DSO.ai 集成 。集成解決方案有助于最大限度地提高系統性能和熱完整性、信號完整性和電源網絡設計的結果質量。

Synopsys 提供最高性能、最低延遲、最低功耗和最小面積的 die-to-die IP 解決方案,包括 UCIe 和專有控制器、物理層設備 (PHY) 和驗證 IP。基于 UCIe 的 IP 符合最新的 UCIe 規范,專有 die-to-die IP 可提供 40Gbps 性能、最大 die-edge 和功率效率、低延遲以及對標準和先進封裝技術的支持。

其 2.5D 和 3D 多芯片解決方案已幫助多個代工工藝實現了多項硅片成功。客戶采用率和代工廠產能持續提升。3DIO 標準也日趨成熟。

出于這些原因以及其他原因,可以相信到 2025 年,至少一半的新 HPC 芯片設計將采用 2.5D 或 3D 多芯片設計。

評論