內存制造技術再創新,大廠新招數呼之欲出

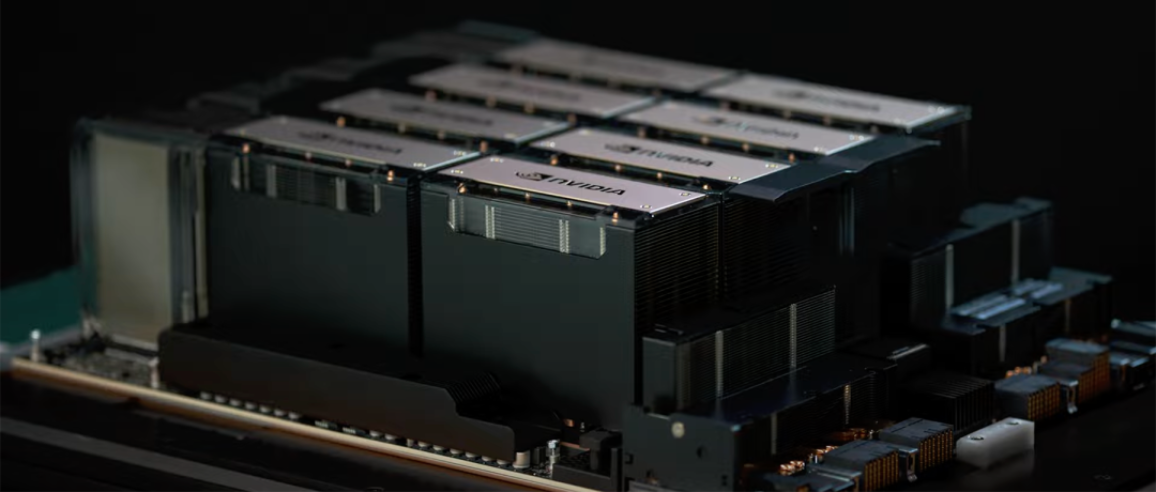

在高性能計算系統,特別是 AI 服務器中,內存(DRAM)的容量和帶寬指標越來越重要,因為處理器需要處理巨量數據,傳統 DRAM 已經無法滿足需求。目前,HBM 是當紅炸子雞。

本文引用地址:http://www.104case.com/article/202407/460748.htm相對于傳統 DRAM,HBM 的制造要復雜很多,它需要將多個 DRAM 裸片堆疊在一起,這就需要用到較為先進的封裝技術了。

隨著技術進步和市場需求的變化,HBM 堆棧的密度也在增加,有機構統計,按照當下的勢頭發展下去,將從 2022 年的 16GB 增加到 2027 年的 48GB,DRAM 大廠美光更加樂觀,預計 2026 年將出現 64GB 的 HBMNext(HBM4),堆疊層數能達到 16,這樣,使用 16 個 32Gb 的 DRAM 裸片就可以構建 64GB 的 HBM 模塊,這需要存儲器制造商進一步縮小 DRAM 裸片的間距,需要用到新的生產技術,特別是更好的封裝技術。

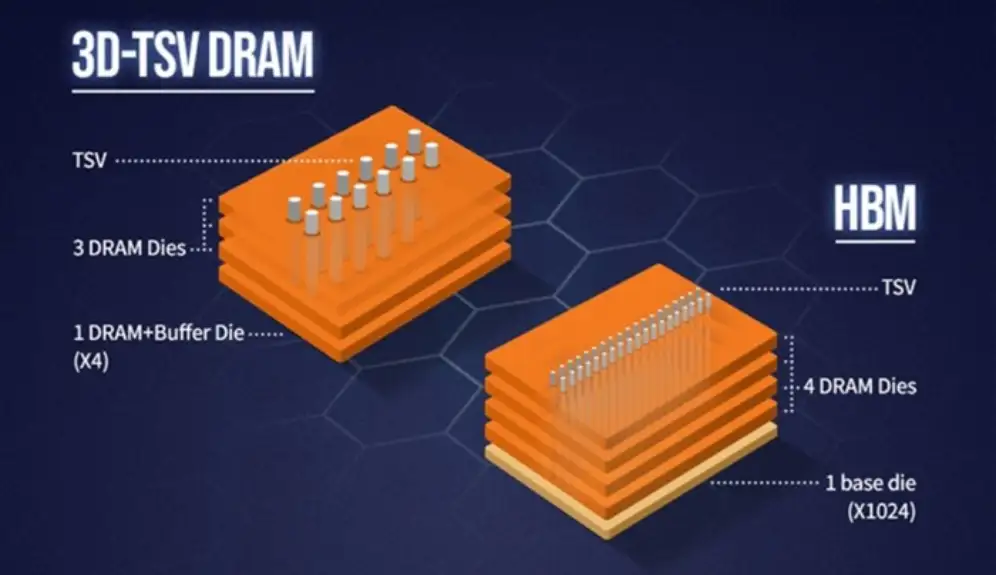

通常情況下,HBM 堆棧使用硅通孔(TSV)垂直連接多個 DRAM 裸片,這種帶有 TSV 的堆疊架構允許非常寬的內存接口(1024 位)、高達 36GB、64GB 的內存容量,并可實現超過 1TB/s 的帶寬。

生產 HBM 堆疊芯片比生產傳統的 DRAM 要復雜得多。首先,用于 HBM 的 DRAM 裸片與典型 DRAM(例如 DDR4、DDR5)完全不同,內存生產商必須制造出足量的 DRAM 裸片,并對它們進行測試,然后將它們封裝在預先測試好的高速邏輯芯片層之上,最后測試整個封裝。這個過程既昂貴又耗時。

以最新量產的 HBM3E 為例,其芯片尺寸大約是同等容量 DDR5 的兩倍,除了邏輯層和 DRAM 層,還需要一個接口層,如此復雜的封裝堆棧,會影響良率。因此,隨著 HBM 的發展,堆疊層數不斷增多,封裝復雜度也在增加,其制造難度越來越大,且良率難以提升。

3D DRAM 接力

HBM 并不是高性能計算系統用內存的最終形態,從各大存儲器廠商的研發方向來看,在存算一體徹底解決「存儲墻」問題、相關芯片技術成熟并實現量產之前,3D DRAM 將是 HBM 的繼任者。

傳統 DRAM 需要復雜的讀寫數據操作流程,而 3D DRAM 可以通過垂直堆疊的存儲單元直接存取和寫入數據,顯著提高了存取速度。3D DRAM 的優勢不僅包括高容量和快速數據訪問,還具有低功耗和高可靠性特點,可以滿足各種應用需求。

這里先簡單介紹一下 DRAM 的基本結構。

DRAM 單元電路由一個晶體管和一個電容器組成,晶體管負責傳輸電流,使信息(位)能夠被寫入或讀取,電容器則用于存儲位。

DRAM 由被稱為「位線 (BL)」的導電材料組成,位線提供注入晶體管的載流子(電流)。晶體管就像一個閘門,可以打開(接通)或關閉(斷開),以保持或停止電流在器件內的流動。這種柵極狀態由施加在被稱為「字線 (WL)」的接觸導電結構上的電壓偏置來定義,如果晶體管導通,電流將流過晶體管到達電容器,并存儲在電容器中。

電容器需要有較高的深寬比,這意味著它的高度遠大于寬度。在一些早期的 DRAM 中,電容器的有源區被嵌入到硅襯底中,在最近幾代 DRAM 中,電容器則是在晶體管頂部進行加工。

3D DRAM 是將 DRAM 單元垂直堆疊,是一種具有全新結構的存儲芯片,打破了原有的模式,它有些類似已經成熟的 3D NAND 單元垂直堆疊,但制造難度比 3D NAND 大。3D DRAM 不是簡單地將 2D DRAM 組件堆疊在一起,也不同于 HBM,需要重新設計 DRAM 架構,需要用到一些先進的晶體管制造技術和先進封裝技術。

3D DRAM 設計重點是解決制程節點微縮和多層堆疊的難題,另外,還有電容器和晶體管微縮,以及單元間連接和通孔陣列,還要制定相應的工藝規格。通過垂直堆疊,3D DRAM 芯片將單位面積的容量增加 3 倍。3D DRAM 與 HBM 在設計和制造層面都是不一樣的。

據 The Elec 報道,三星和 SK 海力士都已將混合鍵合確定為未來制造 3D DRAM 的關鍵封裝技術。據悉,三星計劃在 2025 年推出 3D DRAM 芯片,SK 海力士還沒有確定具體時間。目前,三星和 SK 海力士使用微凸塊來連接 DRAM 模塊,混合鍵合技術可以通過使用硅通孔垂直堆疊芯片,以消除對微凸塊的需求,從而顯著減少芯片厚度。

制造 3D DRAM,要解決幾個問題

為了推進 DRAM 制程微縮,需要將 2D DRAM 組件側放并堆疊起來,但這會面臨一些難題:水平方向需要橫向刻蝕,但由于凹槽尺寸差異很大,橫向刻蝕非常困難;在堆棧刻蝕和填充工藝中需要使用不同的材料,這給制造帶來了困難;連接不同 3D 組件時存在集成難題。

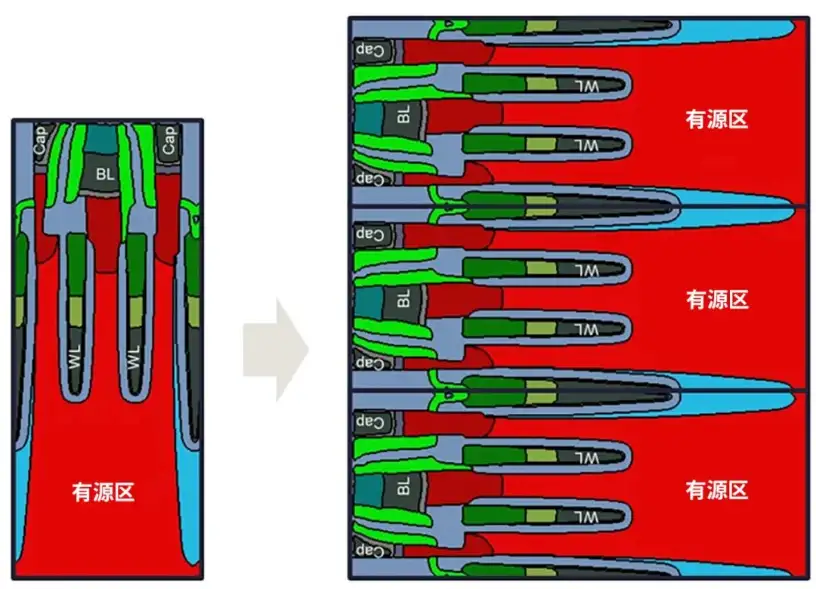

在制造 3D DRAM 時,需要縮短電容器 (Cap) 的長度(電容器的長度不能和高度一樣),并進行堆疊,以提升單位面積的存儲單元數量。

圖:2D DRAM 架構垂直定向視圖(左圖),將其翻轉并將結構堆疊在一起(右圖)的做法不可行的主要原因是需要刻蝕橫向空腔,并將其以不同的橫向深度填充到硅有源區中。

上圖表示的結構不變,將其順時針旋轉 90 度,結構將處于自上而下的視圖中。在這個方向上,可以堆疊納米薄片。但是,這種情況下,原始設計顯示的區域非常密集,因此,位線和電容器需要自上而下地進行工藝處理,并且距離很近。要實現這種方向的 3D 堆疊,需要重新設計架構。

除了要設計新架構,還必須改變 3D DRAM 的金屬化和連接性,需要設計新方法來促使電流通過中央的位線堆疊,包括連接各層的水平 MIM(金屬-絕緣層-金屬)電容器陣列,以及將柵極包裹在晶體管周圍(柵極全包圍)。其原理是,當電流通過時,只有目標位線(層)被激活,在被激活的層中,電流可以連接到正確的晶體管。

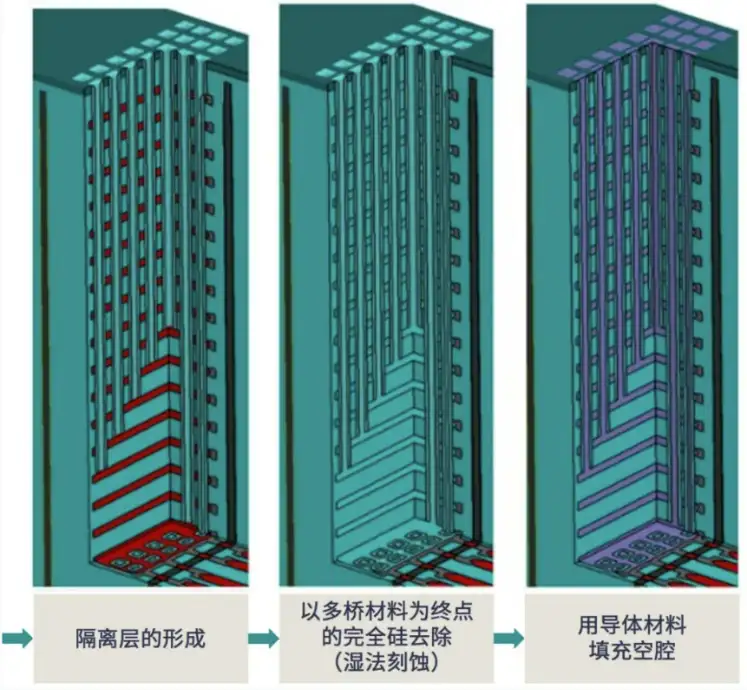

還有硅通孔陣列問題。為了避免 3D NAND 中使用的臺階式結構的局限性,需要引入穿過硅堆棧層且可以在特定層停止(每層一個通孔)的通孔陣列結構,將接觸點置于存儲單元內部。溝槽制作完成后,可以引入只存在于側墻的隔離層。

高溝槽用于引入刻蝕介質以去除硅,然后在空溝槽中引入導電金屬。其結果是,頂部的每個方格(下面最后三張圖片中的淺綠色和紫色方框)只與下面的一層連接。

工藝方面,需要獨特且創新的工藝,3D DRAM 是一種前沿設計,要想實現量產,采用的工藝和設計是從未見過或嘗試過的。

3D 封裝助陣

以上介紹的是 3D DRAM 在芯片設計和制造工藝方面的挑戰和解決思路,相應的裸片制造出來后,需要更適合、更先進的封裝技術,將這些 DRAM 裸片和邏輯等功能部分有機地結合在一起,才能使應用效能最大化。

越需要用到先進封裝的地方,說明被封裝的裸片越小,封裝在一起的整體復雜度越高,3D DRAM 則充分涵蓋了這兩點。先進封裝包括 2.5D 和 3D 封裝,2.5D 難以滿足 3D DRAM 封裝要求,必須采用垂直堆疊超小型構建塊(DRAM 裸片),并通過硅通孔實現互連的 3D 封裝。

在 2.5D 封裝中,邏輯單元、內存或其它類型的芯片使用倒裝芯片方法水平堆疊在硅中介層上,用微凸塊連接不同芯片的電子信號,通過中介層中的硅通孔連接到下面的金屬凸塊,然后封裝到 IC 基板上,在芯片和基板之間建立更緊密的互連。從側面看,雖然芯片是堆疊的,但本質仍然是水平封裝(傳統芯片封裝都是水平的)。不過,與傳統封裝相比,2.5D 封裝中的裸片大小和間距小了很多,接近 3D 封裝。

3D 封裝要將多個裸片(面朝下)堆疊在一起,直接使用硅通孔垂直堆疊,將上方和下方不同裸片的電子信號連接起來,實現真正的垂直封裝。目前,越來越多的 CPU、GPU 和內存開始采用 3D 封裝技術。

到了 3D 封裝階段,混合鍵合技術幾乎是必選項。

混合鍵合是芯片封裝工藝中使用的芯片鍵合技術之一,常用的商用技術是「Cu-Cu 混合鍵合」。使用 Cu-Cu 混合鍵合,金屬觸點嵌入到介電材料中,通過熱處理工藝,這兩種材料結合在一起,利用固態銅金屬的原子擴散來實現鍵合。這種方法解決了以前倒裝芯片鍵合工藝中遇到的挑戰。

混合鍵合不是唯一的先進封裝技術,但它提供了最高密度的垂直堆疊。封裝中的微凸起占用的體積使得堆棧太高,無法放入帶有 GPU 或 CPU 的封裝中,混合鍵合不僅會縮小 DRAM 裸片的高度,還可以更容易地從封裝中去除多余的熱量,因為這種封裝各層之間的熱阻較小。

與倒裝芯片鍵合相比,混合鍵合具有多種優勢,它允許實現超高的 I/O 數量和更長的互連長度,通過使用介電材料代替底部填料進行粘接,消除了填充成本。此外,與晶圓上的芯片鍵合相比,混合鍵合的厚度最小,這對于需要堆疊多層芯片的 3D DRAM 封裝特別友好,因為混合鍵合可以顯著降低整體厚度。

三大廠商的 3D DRAM 制造進展

目前,三星、SK 海力士和美光這三大存儲芯片廠商都在研發 3D DRAM,相應的制造工藝和封裝技術也在同步開發中。

美光從 2019 年起就開始了 3D DRAM 的研究,擁有 30 多項與 3D DRAM 相關的專利,獲得的專利數量是三星和 SK 海力士的 2~3 倍。

近些年,三星一直在進行 3D DRAM 的研究,并推出了業界首個 12 層 3D-TSV 技術。

2023 年,在日本舉行的「VLSI 研討會」上,三星電子發表了一篇包含 3D DRAM 研究成果的論文,并展示了 3D DRAM 芯片內部結構的圖像。

據消息人士稱,2023 年 5 月,三星電子在其半導體研究中心內組建了一個開發團隊,大規模生產 4F2 結構 DRAM。由于 DRAM 單元尺寸已達到極限,三星想將 4F2 應用于 10nm 級工藝或更先進制程的 DRAM。如果三星的 4F2 DRAM 存儲單元結構研究成功,在不改變制程的情況下,裸片面積可比現有 6F2 DRAM 存儲單元減少約 30%。

據悉,三星已經將 3D DRAM 堆疊至 16 層。

SK 海力士正在為將來的 DRAM 開發 IGZO 通道材料,它可以改善 DRAM 的刷新特性。據悉,IGZO 薄膜晶體管憑借其適中的載流子遷移率、極低的漏電流以及基板尺寸的可擴展性,在顯示面板行業長期得到應用。它可以成為未來 DRAM 可堆疊通道材料的候選方案。

最近,在夏威夷舉行的 VLSI 2024 峰會上,SK 海力士發布了 3D DRAM 的最新研究成果,其 5 層堆疊的 3D DRAM 良率已達 56.1%。此外,SK 海力士的實驗性 3D DRAM 在性能上已展現出與 2D DRAM 相媲美的特性,但是,在實現商業化之前,仍需進行大量的技術驗證和優化工作。

結語

作為芯片行業的大宗商品,DRAM 本來就具有龐大的市場份額,如今,在高性能計算需求的推動下,各種新的內存技術和產品依次出現,給這一本來就很熱鬧的市場增添了更多看點。

隨著 AI 服務器的發展,HBM 迅速走紅,相關芯片的制造和封裝是當下產業的熱點話題。隨著應用的發展和技術水平的提升,未來幾年,3D DRAM 很可能會替代當下 HBM 的行業地位,因此,相關芯片制造和半導體設備廠商都在研發上投入越辣越多的資源,不斷蓄力。

就芯片制造和封裝而言,3D DRAM 還需要繼續攻關,距離量產還有一段時間。對此,SK 海力士指出,雖然 3D DRAM 有著巨大的發展潛力,但在實現商業化之前仍然需要做大量工作。目前,3D DRAM 表現出的性能特征依然很不穩定,需要達到 32~192 層堆疊的存儲單元才能廣泛使用。

評論