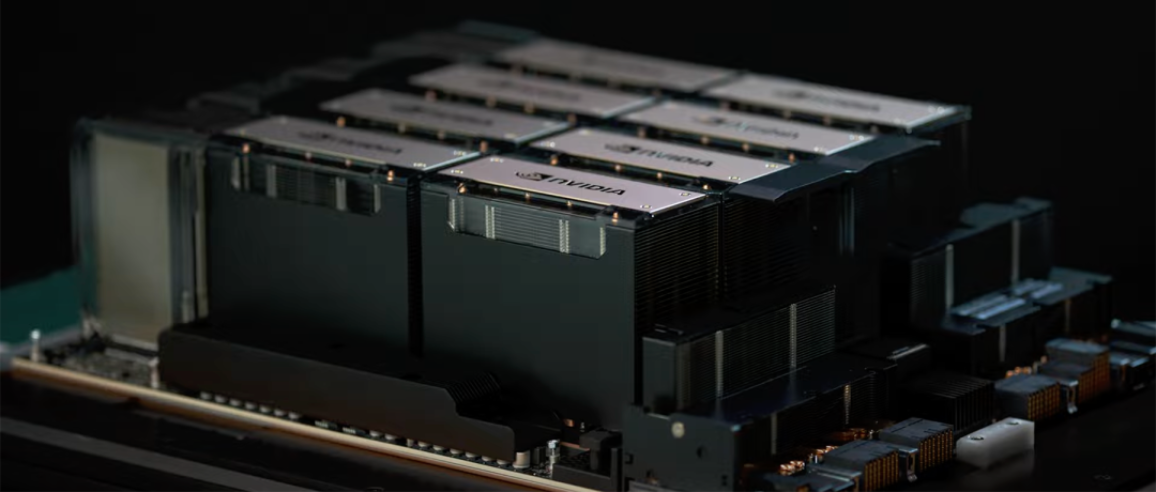

SK海力士試圖用低溫蝕刻技術生產400多層的3D NAND

SK 海力士正在評估東京電子(TEL)最新的低溫蝕刻工具,該工具可在-70°C 的溫度下運行,以實現 400 多層的 3D NAND。據 The Elec 報道,低溫蝕刻工具的「鉆孔」速度是傳統工具的 3 倍,這一功能將有助于制造具有 400 多個活動層的 3D NAND。

本文引用地址:http://www.104case.com/article/202405/458440.htmSK 海力士沒有將實際設備進口到韓國,而是將測試晶圓發送到日本的東京電子實驗室。這種方法使 3D NAND 制造商能夠有效地評估該技術的潛力,而無需將實際工具運送到 SK 海力士并將其安裝到晶圓廠中。新的蝕刻系統在-70°C 的冷卻溫度下運行,這與當前蝕刻工藝的 0°C~30°C 范圍形成鮮明對比。

該報告稱,TEL 的下一代蝕刻機可以在短短 33 分鐘內完成 10μm 深的高縱橫比蝕刻,比現有工具快 3 倍以上。這一成就不僅是一項重大的技術進步,而且大大提高了 3D NAND 生產效率,可以重塑 3D NAND 器件的生產時間表和輸出質量。

在生產 3D NAND 時,有些人可能會說「蝕刻垂直孔」很簡單,但事實并非如此。事實上,蝕刻具有良好均勻性的深存儲器通道孔是一項挑戰,這就是為什么業界采用雙堆疊甚至三重堆疊(構建兩個或三個單獨的堆棧,而不是一個帶有「深」通道孔的堆棧)用于 3D NAND。

SK 海力士的 321 層 3D NAND 產品采用三層疊層結構。隨著 TEL 新型蝕刻設備的采用,可以在單層或雙層堆棧中構建 400 層 3D NAND 器件,這意味著更高的生產效率。未來超過 400 層的產品是過渡到單層還是雙層,將取決于工具的可靠性以及它是否能一致地重現其結果。

TEL 設備的一個顯著環境優勢是它使用氟化氫(HF)氣體,其全球變暖潛能值(GWP)小于 1。與傳統使用的全氟化碳(如四氟化碳(CF4)和八氟丙烷(C4F8))相比,這大大減少了 GWP,它們的 GWP 分別為 6030 和 9540。因此,TEL 新工具的潛在采用反映了行業對更環保制造實踐的日益增長的趨勢。

SK 海力士通過向 TEL 發送晶圓來測試蝕刻工具的同時,三星電子正在通過導入該工具的演示版本來評估相同的技術。這些測試的結果將決定低溫刻蝕技術在半導體制造中的未來采用和潛在標準化。

各大廠商紛紛布局 3D NAND 技術

在 3D NAND 技術推出之前,NAND 閃存均為 2D 平面形式。2D NAND 架構的原理就像是在一個有限的平面上蓋平房,平房的數量越多,容量也就越大。過往存儲芯片廠商將平面 NAND 中的單元尺寸從 120nm 擴展到 1xnm 節點,實現了 100 倍的容量。不過隨著單元尺寸達到 14 納米的物理極限,2D 結構在擴展存儲容量方面有著很大的局限性(當工藝尺寸達到一定階段之后,閃存就很容易因為電子流失而丟失其中保存的數據)。

隨著 2D NAND 的微縮達到極限,2007 年東芝(現在的鎧俠)提出了 3D NAND 結構的技術理念,3D NAND 是行業的一個創新性方向。與減少每個節點單元尺寸的平面 NAND 不同,3D NAND 使用更寬松的工藝,大約介于 30 納米到 50 納米之間,它通過增加垂直層數來獲得更大的存儲容量。因此,我們也可以看到,目前主流的存儲芯片制造商均在競相通過增加 3D NAND 垂直門數,以此來提高存儲密度。他們已經規劃了下一代 3D NAND 產品,包括 232 層/238 層,甚至更大到 4xx 層甚至 8xx 層。雖說都在蓋樓,但是各家蓋樓所采用的架構卻有所不同。

3D-NAND 的層數堆疊,已經成為各大廠商競相追逐的目標。目前主流廠商已經到了第 6 代工藝,Micron 剛剛宣布完成 232L 3D TLC NAND,讀寫性能都得到大幅提升,采用的是雙堆棧技術。

從 Micron 透露的路標來看,對 NAND 技術的研發也是持續投入,爭取一直處于領先的地位,當前主要在 TLC,后續會在 QLC 繼續發力。據了解,Micron 在 PLC NAND 上暫時未打算重點投入,這也跟 PLC NAND 的可靠性需要更大的技術支撐,研發投入更大有關。同樣的工藝研發投入,隨著 bit/cell 的增加,容量的收益卻在下降。

在 Micron 宣布 232 層之后,海力士 Sk Hynix 也接著發布了 238 層 512Gb TLC 4D NAND。海力士這個 4D NAND 叫法,噱頭大于實際意義,實際也是 3D-NAND 的變形,類似 CuA 架構,就是把電路單元放在存儲單元之下 (Peri Under Cell, PUC) 而已.

美光 Micron 和海力士 SK Hynix 發布的 200L+的 NAND,采用的都是 Charge Trap Flash(CTF)。目前市場上,也僅剩 Solidigm(Intel NAND 賣給海力士后新成立的公司) 還在堅持使用 Floating Gate(FG) 架構。與 FG 浮柵不同,FG 浮柵將電荷存儲在導體中,而 CTF 將電荷存儲于絕緣體中,這消除了單元之間的干擾,提高了讀寫性能,同時與浮柵技術相比減少了單元面積。不過,FG 浮柵對 read disturb 和 program disturb 的抗干擾比 CTF 要好,總體來說,CTF 工藝成本更低,這也是大多數公司選擇 CTF 的原因。

國內廠商 YMTC 自研的 Xtacking 技術也到了 3.0,預計也將發布超過 200L 層的 3D NAND,很可能層數在 232 層,采用 6-plane 的設計,相對 4-plane 的架構,性能將得到超過 50% 的提升。

根據目前各家 NAND 原廠的研發狀態,預計在 2025 年,我們將會看到層疊超過 500L 的 3D NAND。甚至在 2030 之前,超過 800L 的 3D NAND 也可能會進入大家的視野。

評論