平面→立體,3D DRAM重定存儲器游戲規則?

近日,外媒《BusinessKorea》報道稱,三星的主要半導體負責人最近在半導體會議上表示正在加速3D DRAM商業化,并認為3D DRAM是克服DRAM物理局限性的一種方法,據稱這將改變存儲器行業的游戲規則。

本文引用地址:http://www.104case.com/article/202303/444657.htm3D DRAM是什么?它將如何顛覆DRAM原有結構?

壹

摩爾定律放緩,DRAM工藝將重構

1966年的秋天,跨國公司IBM研究中心的Robert H. Dennard發明了動態隨機存取存儲器(DRAM),而在不久的將來,這份偉大的成就為半導體行業締造了一個影響巨大且市場規模超千億美元的產業帝國。

DRAM的誕生為PC端、移動端、服務器端等需要處理大容量數據的應用奠定了技術基礎,包括個人電腦(1981年由IBM研發)、智能手機、商用服務器、數據中心、物聯網、云服務等應用領域。從2000年之后,個人電腦、智能手機等應用的爆發式增長,使DRAM在半導體存儲器市場中占據著舉足輕重的地位。

經過數十年的成長,DRAM早已成為半導體主流存儲器之一,并成為了目前最常見的內存產品,還形成了由三星、SK海力士、美光等三大巨頭為主導的市場格局。

從本質上講,DRAM是一種易失性的、基于電容的、破壞性讀取形式的存儲器。DRAM的存儲單元是由一個用于存儲電荷的電容器和一個用于訪問電容器的晶體管組成,由于設計簡潔,因此可以實現極高的集成密度。

DRAM可存儲大量的數據,能在處理數據的同時自行刷新和刪除數據,相比于SRAM,DRAM的成本更低,存儲器密度更高。但DRAM也有一些缺點,比如讀寫速度比SRAM慢,耗電量也較大。并且在現實中,晶體管會有漏電電流的現象,這導致電容上所存儲的電荷數量并不足以正確地判別數據,而導致數據毀損,所以在DRAM工作時,需要定時刷新電路,克服電容漏電問題。

數十年來,摩爾定律一直是業界崇尚的黃金法則,也一直是半導體性能和成本的驅動因素。早前的DRAM可以滿足業界需求,但隨著摩爾定律推進速度放緩,DRAM工藝也步入了技術瓶頸期。

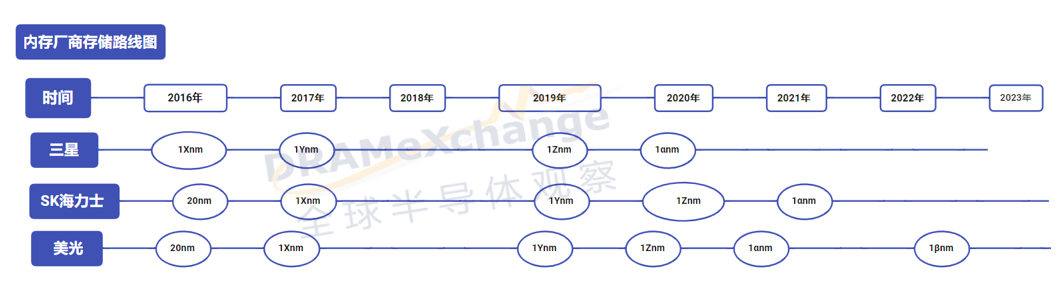

從技術進度上看,目前DRAM芯片工藝已經突破到了10nm級別。2022年11月中旬,美光已實現1β DRAM(第五代10nm級別DRAM)量產,據悉,該公司正在對下一代1γ(gamma)工藝進行初步的研發設計。而三星的技術路線圖預計,2023年進入1b nm(第五代10nm級別DRAM)工藝階段。針對DRAM芯片,隨著晶體管尺寸越來越小,芯片上集中的晶體管就越多,這意味著一片芯片能實現更高的內存容量。

雖然10nm還不是DRAM的最后極限,但多年來DRAM的擴展速度明顯放緩,新的DRAM節點也只是縮小一小部分,3D DRAM順勢成為了存儲廠商迫切想突破DRAM工藝更高極限的新路徑。

貳

平面升立體,3D DRAM跳出原框架

由上文可知,DRAM工藝突破放緩的原因主要在于存儲單元的簡潔結構——由一個用于存儲電荷的電容器和一個用于訪問電容器的晶體管組成。業界的思路也就是顛覆這種結構,并輔以特殊的材料,從而走向創新。

便于增強我們理解這種創新方式的,便是能與DRAM相媲美的存儲器技術NAND Flash,后者早已抵達3D世界,并且如今還跨至4D空間。

當前對于克服DRAM物理局限性有著一定的緊迫性。此前,業界一直在嘗試減小電路線寬,來提高DRAM芯片的密度。通常來說,線寬越小,晶體管越多,集成度越高,功耗越低,速度越快。

此方法的確是達到了效果,但隨著線寬進入10nm范圍,電容器漏電和干擾等物理限制的問題卻明顯增加。為了補救這種情況,業界還引入了high-k材料和極紫外(EUV)設備等新材料和新設備。但顯然,在制造10nm或更先進的小型芯片中,現有的這些技術讓芯片制造商顯得心有余而力不足。

在大環境需求和供給的沖突逼迫下,讓DRAM平面2D升至3D逐漸成為了業界追求技術突破的共識。

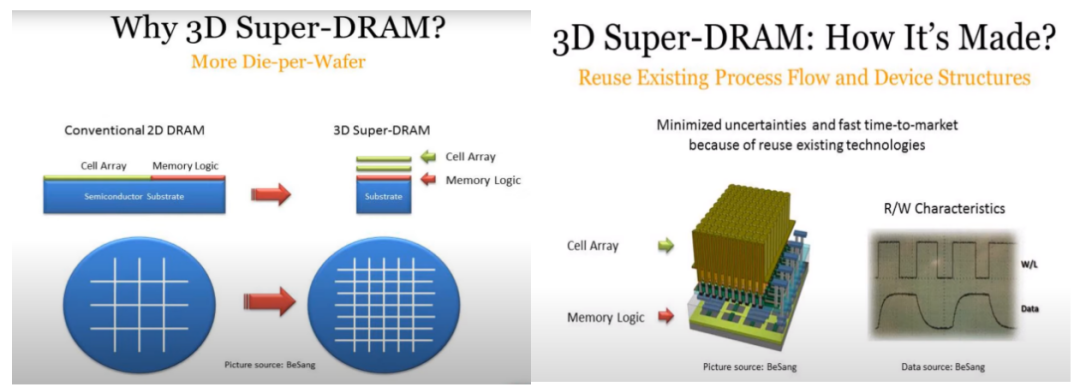

所謂3D DRAM,其實是一種將存儲單元(Cell)堆疊至邏輯單元上方的新型存儲方式,從而可以在單位晶圓面積上實現更高的容量。

針對3D DRAM的構想,BeSang公司曾經向外公布了3D Super-DRAM技術方案。據官網介紹,平面DRAM是內存單元數組與內存邏輯電路分占兩側,3D DRAM則是將內存單元數組堆棧在內存邏輯電路的上方,因此裸晶尺寸會變得比較小,每片晶圓的裸晶產出量也會更多。

△圖片來源:BeSang

而平面DRAM的工藝微縮會越來越困難,其中的關鍵要素是儲存電容的高深寬比。通常來說,儲存電容的高深寬比會隨著組件工藝微縮而呈現倍數增加。所以從原理上看,3D DRAM可以有效解決平面DRAM當前的困境。

而令業界關心的成本問題,3D DRAM使用的3D堆棧技術將實現可重復使用儲存電容,可有效降低單位成本。未來,DRAM從傳統2D發展至3D立體,將是大勢所趨,這對于存儲器市場來說,也將迎來一種擁有全新結構的存儲芯片。

叁

未來增長動力,大廠在蓄力3D DRAM

新技術發展前期,大都是艱難而緩慢的,然而這并不能阻擋企業追逐創新技術的步伐。在技術布局方面,美光早已開始部署3D DRAM的研發,是目前3D DRAM專利數較多的。

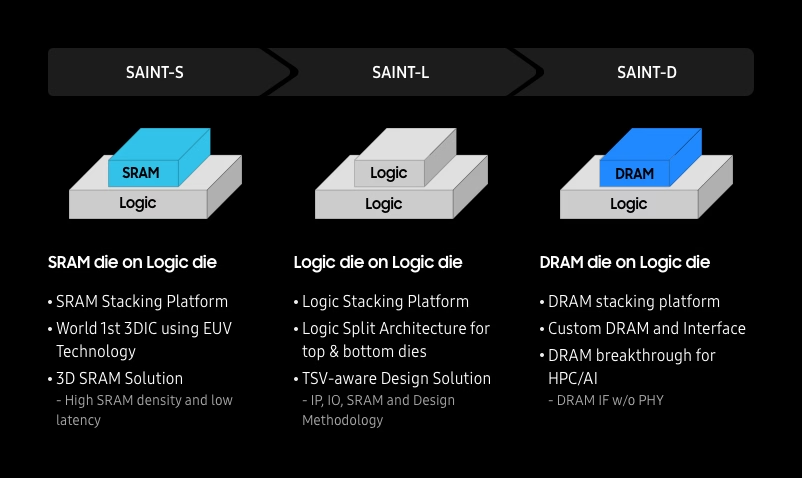

而三星于2021年在其DS部門內建立了下一代工藝開發研究團隊,開始研究。在2022年SAFE論壇上,三星列出了Samsung Foundry 的整體3DIC歷程,并表示將準備用一種邏輯堆棧芯片SAINT-D,來處理DRAM堆疊問題,其設計目的是想將八個HBM3芯片集成到一個巨大的中介層芯片上。近期,三星高管表示正在加速3D DRAM的商業化。不過,目前上述企業都沒有披露該技術的更多信息。

△圖片來源:三星官網

通往3D DRAM道路的技術中,這里要特別提到的是HBM(High Bandwidth Memory,高帶寬存儲器)和無電容式IGZO(indium-gallium-zinc-oxide)技術。

HBM方面,2014年,AMD、SK海力士共同開發出HBM技術,該技術使用TSV(Through Silicon Via,硅穿孔)技術將數個DRAM芯片堆疊起來,大幅提高了容量和數據傳輸速率,自此便開啟了DRAM 3D化發展道路。

后期在三星、美光、NVIDIA、Synopsys等企業的加速競賽下,HBM內存技術已從HBM、HBM2、HBM2E升級至HBM3標準(第四代HBM)。

TrendForce集邦咨詢認為,AI需求持續帶動HBM存儲器成長,并預估2023~2025年HBM市場年復合成長率有望成長至40~45%以上。

IGZO方面,2004年,IGZO氧化物被東京工業大學的細野教授發現并發表在《自然》雜志上。在2020 IEDM(International ElectronDevices Meeting)上,美國和比利時的獨立研究小組IMEC展示了無電容器DRAM。

據當時消息顯示,這款DRAM具有兩個IGZO-TFTs,沒有存儲電容,這種2T0C(2 Transistor -0 Capacitor) DRAM架構有望克服經典1T1C DRAM密度縮放的關鍵障礙,即小單元中Si晶體管的大截止電流尺寸,以及存儲電容器消耗的大面積。在2021 IEDM上,IMEC再次展示了無電容DRAM,在第一次的基礎上進行了改進,保留率和耐久性都有了提高。

同時,據中科院微電子研究所的官網信息顯示,在2021 IEDM上,中科院微電子研究所李泠研究員團隊聯合華為/海思團隊首次提出了新型CAA。該結構有效減小了器件面積,且支持多層堆疊,通過將上下兩個CAA器件直接相連,每個存儲單元的尺寸可減小至4F2,使IGZO-DRAM擁有了密度優勢。

2022年,華為與中科院微電子研究所聯合提出基于基于銦鎵鋅氧IGZO-FET(由In、Ga、Zn、O組成的透明氧化物)的CAA(Channel-All-Around)構型晶體管3D DRAM技術,此成果有望克服傳統1T1C結構DRAM的微縮挑戰。

2023年1月,針對平面結構IGZO-DRAM的密度問題,中科院微電子所微電子重點實驗室劉明院士團隊在垂直環形溝道結構(CAA)IGZO FET的基礎上,研究了第二層器件堆疊前層間介質層工藝的影響,驗證了CAA IGZO FET在2T0C DARM應用中的可靠性。該研究成果有助于推動實現4F2 IGZO 2T0C-DRAM單元。

業界認為,HBM的出現開啟了DRAM 3D化發展道路,無電容IGZO-DRAM也成為了實現高密度3D DRAM的合適候選者。但很多技術現還在探索中,最終能否使DRAM實現3D堆疊,開始新的技術方向,還暫未可知。

不過,從工藝上看,三星當前量產的最尖端DRAM線寬為12nm工藝,美光已經量產了10nm DRAM芯片。考慮到目前DRAM線寬微縮至10nm將面臨的情況,業界認為3~4年后新型DRAM商業化將成為一種必然,而不是一種方向。

從應用領域上看,近年來,雖然消費終端市場的蕭條讓存儲器市場步入冬季,但汽車電子、AI服務器等其他領域對存儲器的需求仍然不缺。而針對新型DRAM的未來,三星電子半導體研究所副社長兼工藝開發室負責人Lee Jong-myung于3月10日在韓國首爾江南區三成洞韓國貿易中心舉行的“IEEE EDTM 2023”上表示,3D DRAM被認為是半導體產業的未來增長動力。

目前3D DRAM的市場格局暫不清晰。總體而言,對DRAM芯片來說,3D DRAM將是一個新的起點,對存儲商來說,這是一次可以搶占下一個戰略高地的機會。

評論