在嵌入式視覺系統設計中使用萊思 CrossLink FPGA 支持 MIPI

| 目錄 | ||

| 第一部分 | | | 嵌入式視覺的發展趨勢 |

| 第二部分 | | | MIPI簡介 |

| 第三部分 | | | 在嵌入式視覺中使用FPGA |

| 第四部分 | | | CrossLink FPGA簡介 |

| 第五部分 | | | 應用案例 |

| 第六部分 | | | 使用CrossLink FPGA進行設計 |

| 第七部分 | | | 設計流程 |

| 第八部分 | | | 小結 |

| 第九部分 | | | 參考資料 |

過去幾年里,嵌入式視覺應用大量涌現,包括從相對簡單的智能視覺門鈴到執行隨機拾取和放置操作的 復雜的工業機器人,再到能夠在無序、地形不斷變化的環境中導航的自主移動機器人(AMR)。快速采 用嵌入式視覺技術的行業包括汽車、消費電子、醫療、機器人、安防/監控以及大量工業應用。

如今,嵌入式視覺正逐漸應用于人工智能(AI)和機器學習(ML)系統中,用來分析圖像和視頻流、檢測/ 識別人和物體以及從看到的景象中提取信息,便于采取下一步行動(關于AI、ANN、ML、DL和DNN的常見 問題1)。

本文首先介紹了當今嵌入式視覺設計一些趨勢。然后探討了現場可編程邏輯門陣列(FPGA)在嵌入式 視覺系統中的應用。最后討論了使用萊迪思半導體的CrossLink? FPGA創建嵌入式視覺系統。

嵌入式視覺的發展趨勢

推動嵌入式視覺設計的主要趨勢有:高分辨率和高帶寬的需求持續增長,系統中視覺傳感器和顯示器的數 量與日俱增,以及小尺寸和低功耗的要求不斷涌現。此外,將人工智能(AI)和機器學習(ML)功能加入 嵌入式系統也是大勢所趨,尤其是添加到靠近視覺傳感器的本地端。

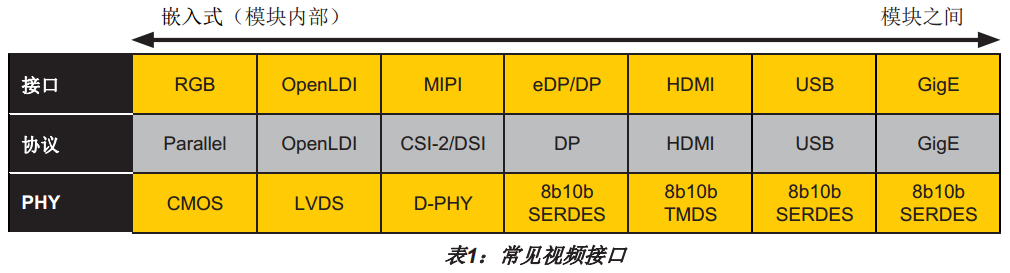

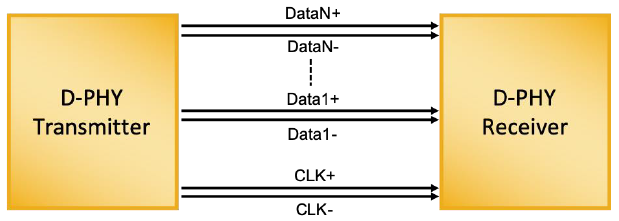

嵌入式視覺系統的另一個趨勢是接口標準的數量和種類不斷增長。表1列出了一些最常見的接口類型。 其中用于“模塊內部”(inside the box)的標準(如設備內部)通常要求驅動幾厘米到幾十厘米大小的 設備,而“模塊之間”(box-to-box)的接口可能需要在幾米到幾百米甚至更大的設備間驅動視覺數據。

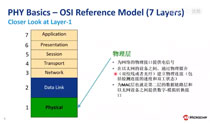

PHY這個術語是“物理層”的縮寫,通常是在芯片上或者作為芯片(集成電路)實現的一種電子電路。 PHY用于實現開放系統互連(OSI)模型的物理層功能,無論計算或電信系統底層內部結構和技術如何,該 模型都能對其通信功能進行標準化。

圖1:PC和智能手機出貨量(資料來源:萊迪思半導體和行業分析師)

MIPI簡介

嵌入式視覺應用中MIPI的使用日益增多,尤其是CSI-2(攝像頭/傳感器)和DSI(顯示屏)協議,兩者均采用被稱之為D-PHY的PHY。在帶寬和接口長度方面,MIPI在位于OpenLDI和eDP/DP(eDisplay Port和Display Port)之間。

MIPI聯盟是一家在全球擁有250名企業會員的國際組織。ARM、英特爾(Intel)、諾基亞(Nokia)、三星(Samsung)、意法半導體(STMicroelectronics)和德州儀器(Texas Instruments)于2003年創建MIPI聯盟,彼時MIPI是“移動產業處理器接口”的英文首字母縮略詞。然而,如今該組織的各類規范不僅適用于處理器互連,更能滿足一臺設備上全部接口需求,所以MIPI不僅僅是首字母縮略詞,而是已經作為單獨的名稱使用。

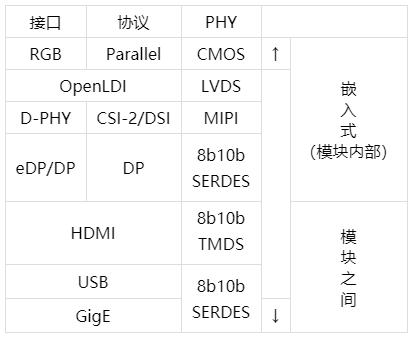

為了了解更多有關MIPI流行的背景信息,我們不妨回顧一下1990年代中期個人計算機(PC)剛開始流行的時期(圖1)。當時的PC使用的接口是外設部件互連標準(PCI)和通用串行總線(USB)。這些低成本的PCI和USB技術隨后被各類不同的產品采用。

MIPI CSI-2和DSI-2協議也是如此,它們最初用于智能手機。自從2007年發布首款iPhone以來,智能手機急速增長,遠遠超過PC。這推動了規模經濟,低成本的攝像頭、顯示屏和處理器組件開始涌現,它們開始廣泛用于各類非智能手機應用和市場。(本文中的“處理器”可能是指SoC芯片、ASSP和應用處理器等器件)

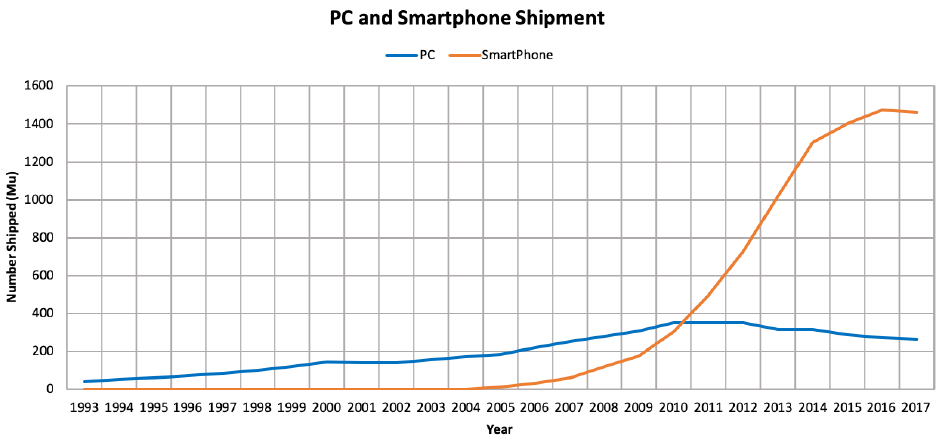

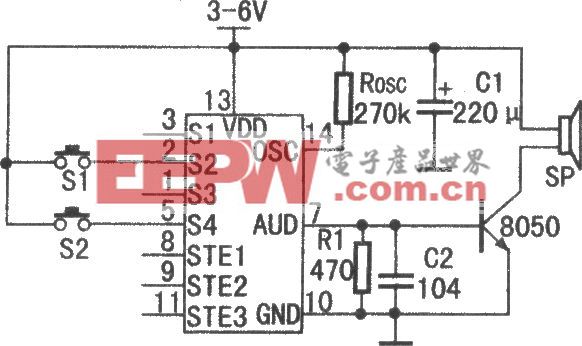

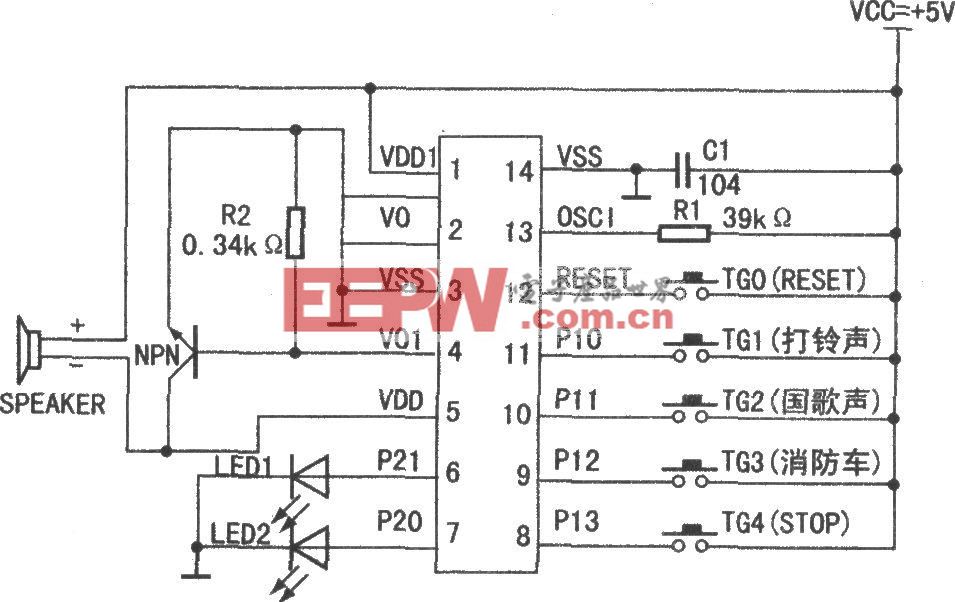

MIPI采用的D-PHY接口(如圖2所示)使用一個差分時鐘和一到四個差分數據通道,支持的速度為80 Mbps到2.5 Gbps。

IPI接口支持兩種運行模式:高速(HS)和低速(LP)。該接口在發送器和接收器之間主要是單向傳輸,但是在某些低速通信情況下,能夠從接收器向發送器傳輸。

圖2 MIPI D-PHY接口

在嵌入式視覺設計中使用FPGA

嵌入式視覺設計的一個重要特征是其架構通常需要不斷調整以適應各種規范的變化,這就讓FPGA成為實現這類設計的理想選擇。

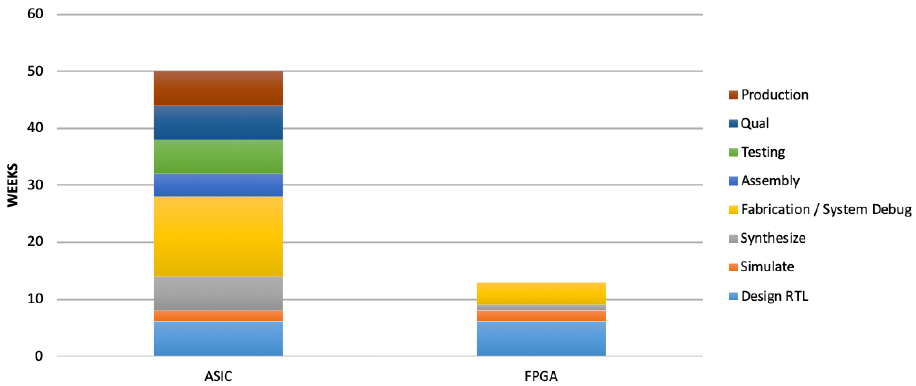

一個主要的考慮因素就是ASIC/ASSP和FPGA設計開發周期的差別,使用FPGA來實現設計(圖3),可加快產品上市(從而快速盈利)。

中型ASIC/ASSP從設計到量產其開發周期要將近一年。此外,由于設計規范不斷發生變化,期間還存在諸多風險(在嵌入式視覺設計中非常常見),再加之ASIC/ASSP的設計流程大多錯綜復雜,這就意味著某個流程出現耽擱,會對其他流程產生連鎖的負面反應。

若采用FPGA實現設計,設計人員可采用經過市場檢驗的硬件,在現場重新配置,應對任何設計規范的變更。

從設計人員的角度來看,開發周期的最初階段(即在抽象的RTL階段捕獲設計)都是相同的,其余步驟要么相似,要么所需時間和資源更少,要么根本不需要。因此使用FPGA的總體優勢是可以在大約三分之一的開發時間內實現設備的正常工作。

從歷史角度看,一些嵌入式系統的設計人員認為FPGA是大尺寸、高功耗的器件,僅僅用于數據中心、通信中心、醫學成像以及軍事等大型應用。

這些傳統的FPGA通常有幾十萬LUT,功率高達50-100 W,封裝尺寸可達55 x 55 mm,通常配置散熱片。然而還有一些專門實現特定功能的FPGA產品,專注于要求小尺寸和低功耗的應用。例如萊迪思半導體提供這類小尺寸(從10 x 10 mm,功耗1 W到1.4 x 1.4 mm,功耗僅為1 mW)的FPGA產品,滿足那些要求小尺寸和高能效應用的需求。

與小型ASIC/ASSP相比,這些功能導向的FPGA更容易快速開發、使用更靈活。此外,由于大多數通用FPGA旨在應用于工業和汽車等多個市場,它們通常都支持商用和工業溫度環境。而ASIC/ASSP大多被開發用于消費電子產品,對此類溫度環境的支持不太普遍。

圖3 使用FPGA加速產品上市和盈利

CrossLink FPGA簡介

萊迪思半導體主要提供四種FPGA產品系列:ECP?、MachXO?、iCE?和CrossLink?。ECP系列包括了設計人員所一般認為的“傳統” FPGA——主要針對互連和加速應用的通用器件。MachXO FPGA具有數百個可編程輸入/輸出(I/O),非常適合需要GPIO擴展、接口橋接和電源管理功能的各類應用。iCE系列是尺寸最小的超低功耗FPGA,最小型號封裝尺寸僅為1.4 mm x 1.4 mm,提供18個I/O。

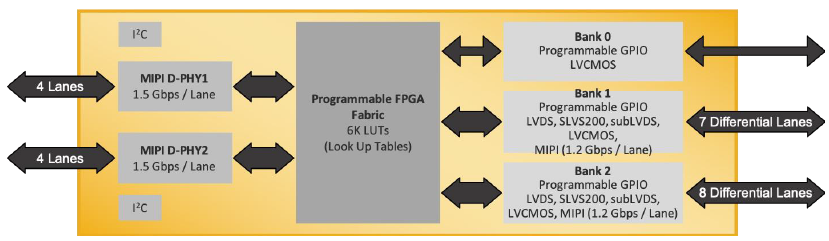

尤其值得一提的是針對高速視頻和傳感器應用進行了優化的CrossLink FPGA。CrossLink FPGA通過硬核PHY增強了其傳統的可編程架構,提供業界最快的MIPI D-PHY橋接解決方案,支持高達12 Gbps和4K UHD分辨率(圖4)。此外,CrossLink器件提供2.46 x 2.46 mm的WLCSP小型封裝和0.4 mm、0.5 mm和0.65 mm球間距的BGA封裝。

CrossLink FPGA提供兩個4通道MIPI D-PHY收發器,每個PHY速率達6 Gbps,還提供15個可編程源同步I/O對,通過LVDS、SLVS200、subLVDS、LVCMOS和OpenLDI(OLDI)等接口標準實現攝像頭和顯示屏互連。此外,這些可編程I/O可實現每通道速率最高1.2 Gbps的“軟MIPI”接口,而LVCMOS可用于在本地實現并行/RGB接口。

圖4 用于嵌入式視覺的CrossLink FPGA包括硬核MIPI D-PHY,優化性能和設計

應用案例

CrossLink FPGA的應用包括傳感器橋接、傳感器復制、傳感器聚合、顯示屏橋接和分屏。這里的“橋接”是指將視頻信號從一種接口標準轉換為另一種。

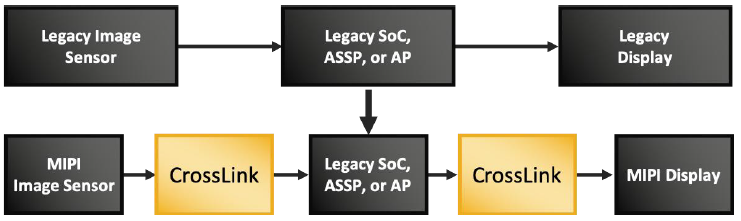

在現有控制器上使用MIPI傳感器和顯示屏:一個典型的案例就是現有系統的SoC、ASSP或AP不支持MIPI,但是設計人員希望在保留原有處理器(及代碼)的同時對系統進行升級,新增更為高效、低功耗、基于MIPI的傳感器和/或顯示屏(圖5)。

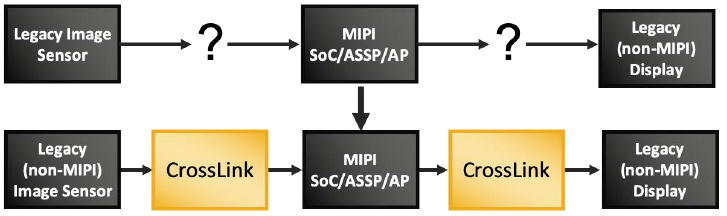

在現有傳感器和顯示屏上使用MIPI控制器:當設計人員的SoC、ASSP、AP支持MIPI,但是又希望使用原本的非MIPI傳感器和顯示屏系統時,也會面臨同樣的問題。工業領域的許多圖像傳感器和顯示屏都采用LVDS、SUBLVDS或并行接口。此外,許多傳統的傳感器采用的是全局快門而非卷簾快門。這就推動了對更為復雜的橋接解決方案的需求。

圖5 使用CrossLink FPGA讓現有的SoC、ASSP、AP兼容MIPI傳感器和/或顯示屏

圖6 使用CrossLink FPGA讓MIPI接口的SoC、ASSP、AP兼容現有的非MIPI傳感器/或顯示屏

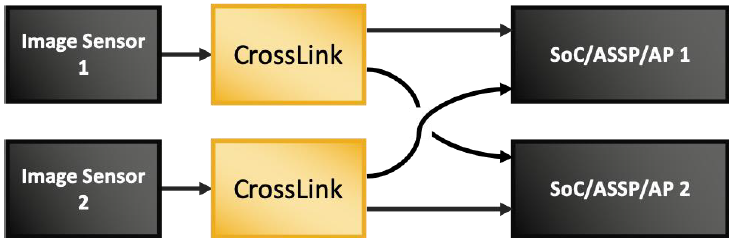

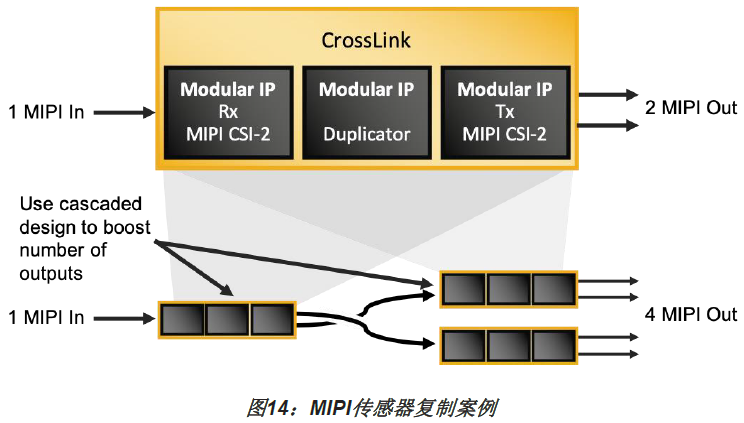

傳感器數據復制:該應用的一個典型案例是,對安全性要求高的應用需要進行數據備份(如智能汽車),因此來自傳感器的視頻輸入可能需要分成兩個數據流,饋送到兩個單獨的處理器中(和許多其他接口標準一樣,MIPI是點對點的,因此不能將單個傳感器直接連接多個處理器)。

這類應用的思路是,如果其中一個處理器發生故障,必須要有數據備份。此外,如果有多個傳感器,每個傳感器的數據流都可以被拆分并饋送到多個處理器。當然,傳感器復制可與橋接功能結合使用。圖7展示了一種可能的配置場景。

圖7 使用CrossLink FPGA在對安全性要求高的系統中實現傳感器數據復制

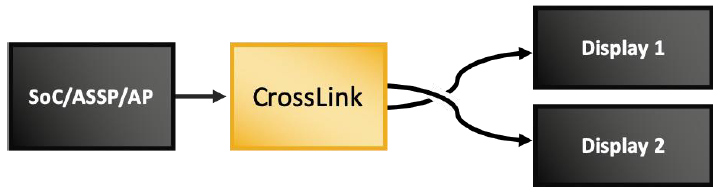

顯示器分屏:當我們需要獲取由系統處理器生成的視頻信號,并將該信號拆分連接到多個顯示屏時,就需要用到顯示器分屏的功能。它可以與橋接功能結合使用。圖8展示了一種可能的配置場景。

圖8 使用CrossLink FPGA實現顯示器分屏

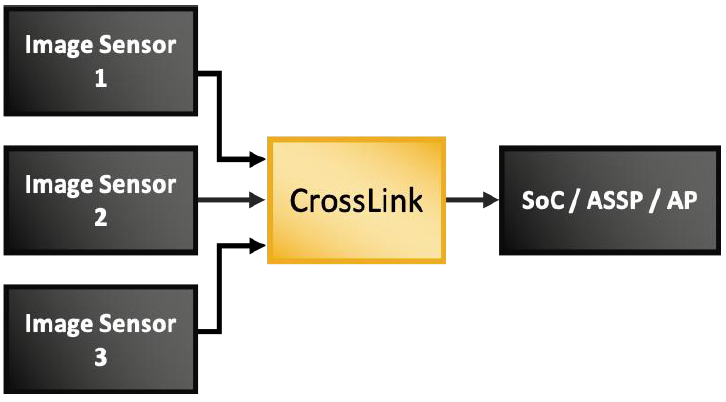

傳感器聚合:最后,我們來談談傳感器聚合應用。正如本文以上所述,這一應用得以發展是因為系統中添加了越來越多的圖像傳感器。問題在于某些處理器的傳感器輸入數量有限,因此我們需要某種方式來聚合來自多個傳感器的數據。

當然,與傳感器復制和顯示屏分屏一樣,傳感器聚合也可以和橋接功能一起使用。

圖9 使用CrossLink FPGA實現傳感器聚合

使用CrossLink FPGA進行設計

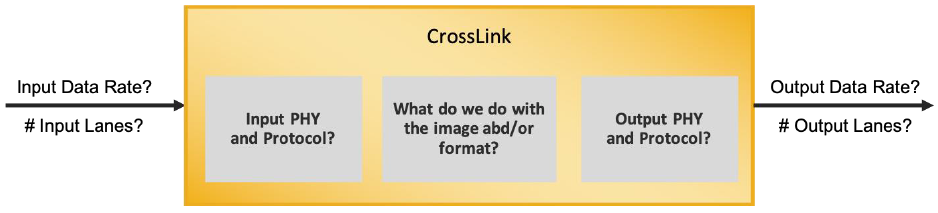

使用CrossLink FPGA進行設計時,要先問自己一些基本的問題,然后順著答案設計基本架構。例如,你打算使用什么PHY和協議來輸入輸出視頻信號(圖10)?

圖10 作出架構方面的決定

這些決定大多和你所選擇的傳感器和顯示屏類型有關(或者因為沒得選擇不得不使用這些類型)。還有一些影響因素就是即將使用的SoC/ASSP/AP處理器類型。反過來,對于上述問題的答案也會引導你思考如何處理圖像及其格式,包括是否要進行復制、聚合和拆分等操作。此外,一旦決定了輸入和輸出數據速率,就可以結合PHY和協議的選擇來決定你的設計要求多少輸入和輸出通道。

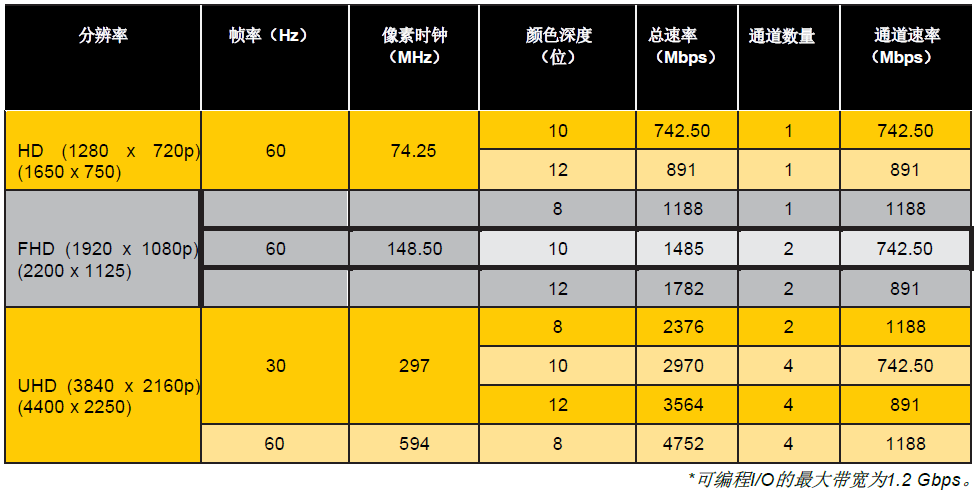

做出架構決策后,就可以根據下表來計算數據速率。例如,假設你選擇60 Hz幀率,色深為10位的全高清(FHD)信號(也稱為“RAW10”),如表2所示。

表2 計算數據速率

我們通常認為FHD的分辨率為1920 x 1080像素,但實際分辨率為2200 x 1125,因為需要在行和幀之間添加消隱周期。計算數據速率的公式為:總速率=水平時鐘*垂直線*幀速率*每像素位數。在我們的示例中,這意味著總數據速率為2200 x 1125 x 60 x 10 = 1485 Mbps(1.485 Gbps)。由于CrossLink可編程I/O的最大帶寬為1.2 Gbps,所以需要使用兩條通道,每條通道的速率為742.5 Mbps。

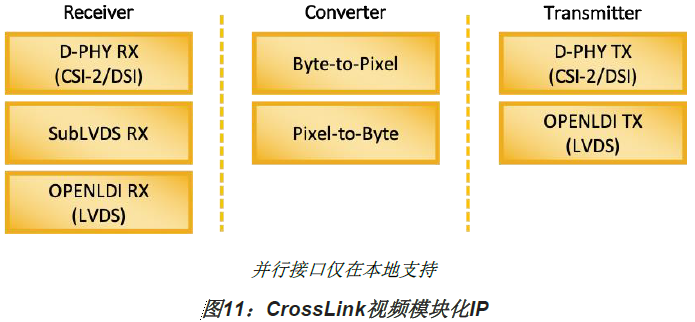

CrossLink FPGA可使用眾多視頻模塊化IP,這些IP可免費使用,主要包括接收視頻數據(Rx)、發送視頻數據(Tx)和時鐘域轉換等(參見圖11)。

大多數設計都使用多個IP模塊作為構建模塊,然后設計人員通過RTL對模塊進行加強。

一些設計人員看到這張圖可能會有這樣的疑問:當CSI-2是用來接收攝像頭傳感器的數據時,為什么還要MIPI CSI-2發送器。同樣,當DSI被用于將數據傳輸到顯示屏時,為什么還要MIPI DSI接收器。答案當然是可能需要執行復制、拆分和/或橋接功能。

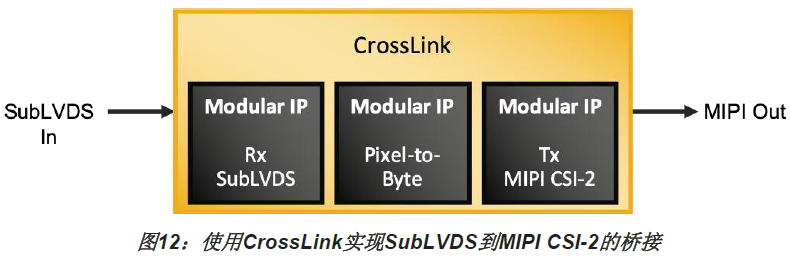

讓我們來看一個簡單的SubLVDS轉MIPI CSI-2橋接案例。在此案例中,我們將使用SubLVDS接收器模塊,像素到字節轉換模塊和MIPI CSI-2發送器模塊(圖12)。

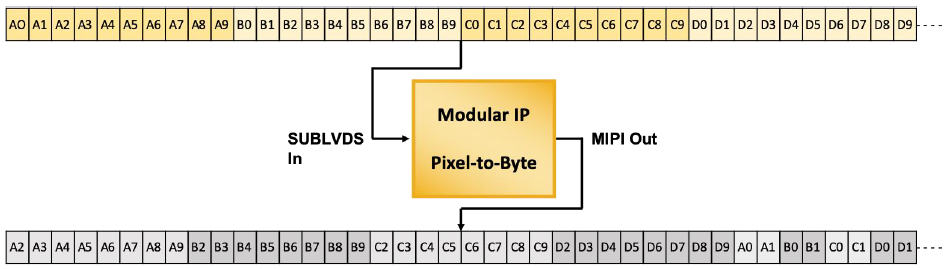

使用像素到字節轉換的原因在于LVDS和MIPI格式的不同。假設SubLVDS輸入的色深為10位(RAW10)。而MIPI格式是基于8位數據包。因此我們需要確定共同的位長,即兩者的最小公倍數,這個案例中就是40位(圖13)。

圖13 使用CrossLink的像素轉字節IP模塊將RAW10轉換為MIPI CSI-2

接下來我們來看一下MIPI傳感器復制的案例。該應用使用了MIPI CSI-2接收器和MIPI CSI-2發送器。當MIPI幀經過CrossLink器件時,我們需要在接收和發送器之間用RTL代碼來復制MIPI幀。如果需要更多輸出,則可以使用多個CrossLink FPGA級聯來實現。

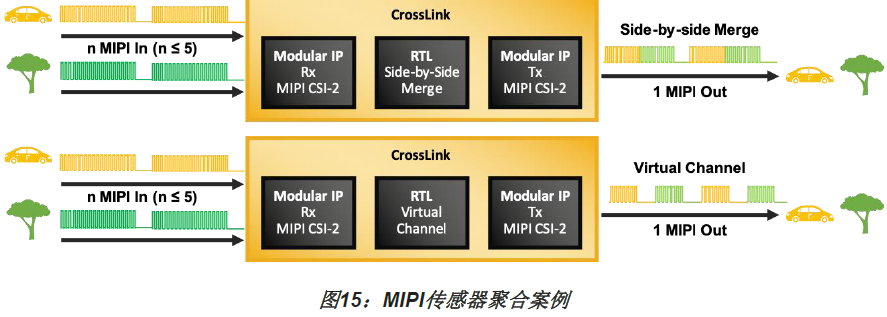

另一個常見的設計要求就是聚合多個視頻傳感器數據流。圖15展示了兩種場景:左右合并和虛擬通道。

兩個例子均為兩個MIPI輸入和一個MIPI輸出。實際上,Crosslink FPGA能夠支持多個(最多5個)MIPI輸入。當有兩個輸入時,輸出數據速率為輸入數據速率的兩倍。

在左右合并的案例中,輸出為線對線合并的圖像。

虛擬通道的概念在MIPI標準中已有定義。MIPI是一種基于數據包的協議,也就是說每個數據包都包含了頭文件和有效數據。在虛擬通道的案例中,我們為每個輸出數據包打上標簽,然后交給下游的SoC/ASSP/AP負責。現階段大多數處理器還無法處理虛擬通道,但是這種方法有望在不久的將來大行其道。

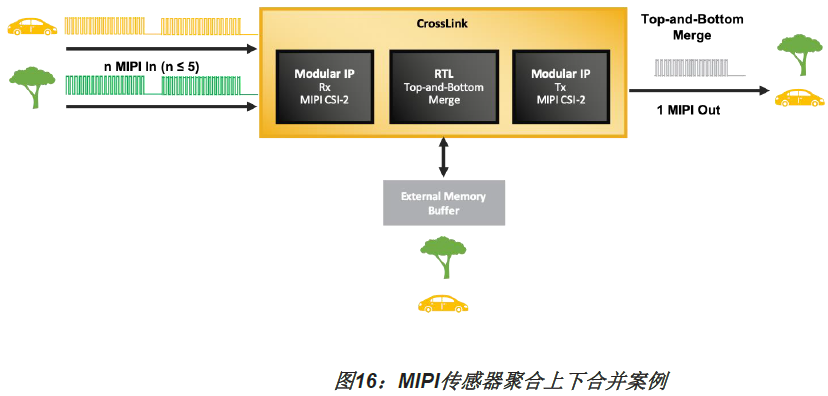

傳感器聚合應用的另一種形式就是上下合并。在此情形下,從設計的角度來看,簡單地讓數據傳輸過去肯定行不通。而是要在通過MIPI發送器輸出之前存儲至少一幀圖像。因此選擇要存儲的幀數和外部緩存的大小就需要另作設計上的考量了。

這里需要注意的是,一旦我們加入外部緩存,除了執行上下合并操作外,還可以進行其他圖像處理操作,如旋轉和/或鏡像。

設計流程

設計流程由以下幾個要素構成(上標數字對應文末的參考來源):

● RTL設計2

● IP庫3

● 模擬2

● 綜合2

● 硬件開發平臺4,5

● 系統調試2

● 額外資源6

你可以使用Lattice Diamond運行RTL代碼、仿真和綜合設計。選擇適當的CrossLink器件后即可啟動項目。你可以在萊迪思Clarity這個IP庫中找到之前討論過的所有CrossLink視頻模塊化IP。只需要在Clarity界面選擇要使用的IP模塊,將其拖放到設計中即可。

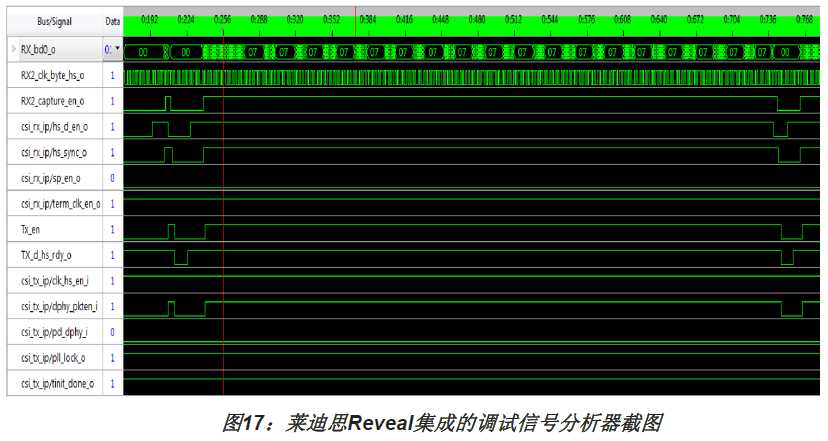

Lattice Reveal能助你調試設計。Reveal具有兩個方面的功能:Reveal Inserter和Reveal Analyzer。Inserter可以定義調試信號發生器,而Analyzer可以將微型邏輯分析器嵌入到設計中,你可以指定觸發條件和要監視的信號。

這些信號發生器和分析器包含在配置位流中,位流已加載到CrossLink器件中。可以使用集成的信號分析器顯示結果(圖17)。

萊迪思還提供多種硬件開發板,包括LIF-MD6000主控連接板,該板載有CrossLink芯片以及用于連接各類傳感器、顯示器和SoC/ASSP/AP器件的連接器。

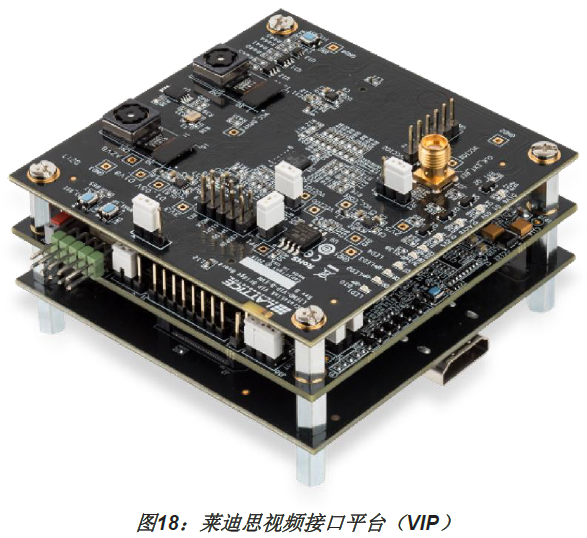

還有視頻接口平臺(VIP),它由三塊開發板組成:具有兩個圖像傳感器的Crosslink VIP輸入橋接板,用作圖像信號處理器的ECP5 VIP板和可用于顯示輸出結果的HDMI VIP輸出板(圖18)。

你還可以選擇其他的開發板,包括HDMI VIP輸入板、DisplayPort VIP輸入板、DisplayPort VIP輸出板和USB3-GbE VIP I/O板。萊迪思提供各類開發板,助您探索和開發基于CrossLink FPGA的嵌入式視覺應用。

最后,萊迪思還提供三套參考設計,展示了下列應用的各個方面:

● N:1MIPI CSI-2虛擬通道聚合7

● MIPI DSI/CSI-2轉OpenLDI LVDS接口橋接8

● SubLVDS轉MIPI CSI-2圖像傳感器橋接9

未來我們將推出更多參考設計,敬請留意萊迪思官網發布的信息。

小結

過去幾年里嵌入式視覺應用極速發展。嵌入式視覺系統的設計人員面臨的挑戰包括:對高分辨率和高帶寬的需求持續增長,系統中視覺傳感器和顯示器的數量與日俱增,以及小尺寸和低功耗的要求不斷涌現。此外,將人工智能(AI)和機器學習(ML)功能加入嵌入式系統也是大勢所趨,尤其是添加到靠近視覺傳感器的本地端。

萊迪思低功耗CrossLink FPGA專為高速視頻和傳感器應用優化。該器件在強化其傳統可編程架構的基礎上,增加了硬核PHY,可提供業界最快的MIPI D-PHY橋接解決方案。

萊迪思的產品組合包括了芯片、IP、參考設計、開發套件和軟件工具,能為嵌入式視覺的設計人員提供靈活的解決方案,如更新接口的標準、高效的視頻信號處理以及硬件加速等。

評論