Vision HDL Toolbox功能增加,適用于高達(dá)8k分辨率的幀尺寸和高幀率視頻

MathWorks近日宣布,隨著 2019b 發(fā)行版的 MATLAB 和 Simulink 產(chǎn)品系列最近上市,Vision HDL Toolbox提供對(duì)在 FPGA 上處理高幀率 (HFR) 和高分辨率視頻的原生多像素流處理支持。視頻、圖像處理和 FPGA 設(shè)計(jì)工程師在處理 240fps 或更高分辨率的 4k 或 8k 視頻時(shí)可以加快權(quán)衡表現(xiàn)和實(shí)現(xiàn)的探索和仿真速度。

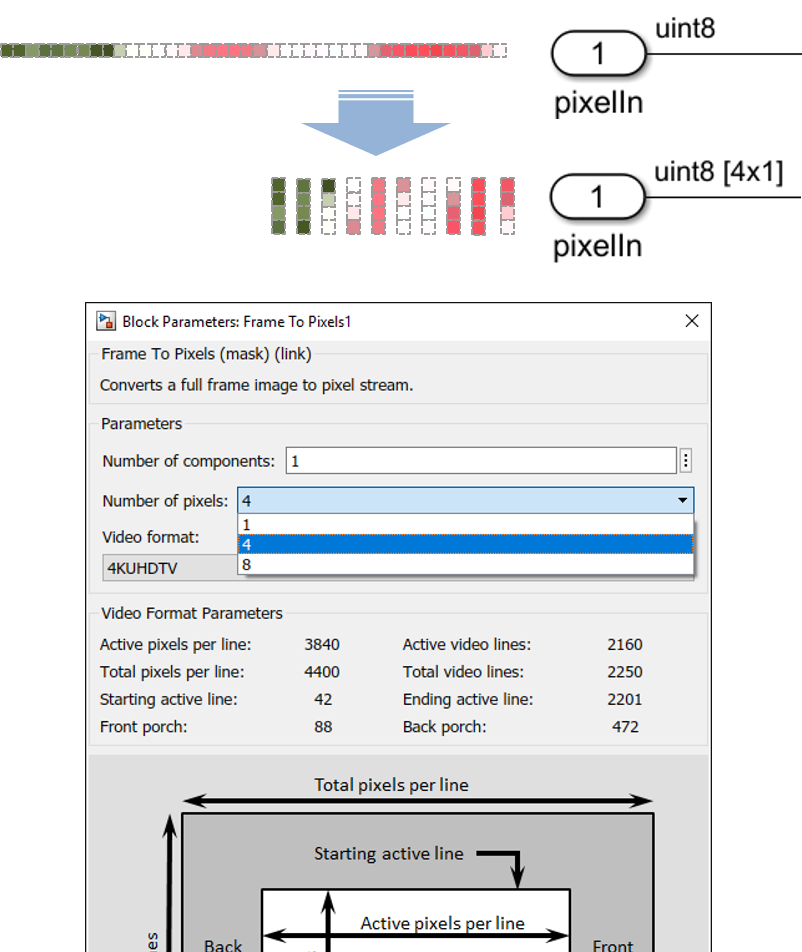

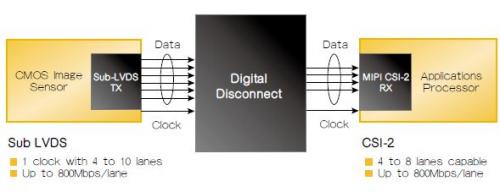

為幫助實(shí)時(shí)處理工業(yè)檢測(cè)、醫(yī)學(xué)成像以及情報(bào)、監(jiān)控、和偵察 (ISR) 等應(yīng)用中的高分辨率和 HFR 視頻而設(shè)計(jì) FPGA 的工程師面臨挑戰(zhàn),力爭(zhēng)達(dá)到吞吐量、資源利用率和功耗等目標(biāo)。Vision HDL Toolbox 提供可以并行處理 4 或 8 像素的模塊,底層硬件實(shí)現(xiàn)自動(dòng)進(jìn)行更新,以通過(guò)指定的并行性支持仿真和代碼生成。這種能力可幫助硬件工程師與圖像和視頻處理工程師合作,在較高的抽象級(jí)別上探索和仿真視覺(jué)處理硬件表現(xiàn)。向此設(shè)計(jì)工作流程中添加 HDL Coder,工程師可以直接從他們已驗(yàn)證的高層次模型生成可合成、獨(dú)立于目標(biāo)的優(yōu)化 VHDL 或 Verilog 代碼。

“在 FPGA、ASIC 和 SoC 設(shè)備上實(shí)現(xiàn)視覺(jué)處理算法需要在吞吐量和資源利用率之間巧妙地權(quán)衡,4k、8k 和高幀率視頻成倍地?cái)U(kuò)大這一挑戰(zhàn)。”MathWorks 的首席產(chǎn)品營(yíng)銷經(jīng)理 Jack Erickson 說(shuō),“探索解決方案空間和在較高的抽象級(jí)別上仿真,可幫助工程師在致力于寄存器傳送級(jí) (RTL) 之前更快速地在架構(gòu)上收斂。Vision HDL Toolbox 及其原生的每時(shí)鐘多像素 (multi-pixel-per-clock) 處理自動(dòng)實(shí)現(xiàn)所有細(xì)節(jié),使工程師能夠?qū)P拈_發(fā)滿足其要求的硬件算法。”

Vision HDL Toolbox 為在 FPGA、ASIC 和 SoC 設(shè)備上進(jìn)行視覺(jué)系統(tǒng)設(shè)計(jì)和實(shí)現(xiàn)提供了像素流處理算法。它提供一個(gè)設(shè)計(jì)架構(gòu),可支持各類接口類型、幀尺寸和幀率。該工具箱中的視頻和圖像處理算法對(duì)硬件實(shí)現(xiàn)進(jìn)行建模,包括延遲、控制信號(hào)和行緩沖區(qū)。

該工具箱算法旨在生成 VHDL 和 Verilog(使用 HDL Coder)的可讀取、可合成的代碼。生成的 HDL 代碼是經(jīng)過(guò) FPGA 驗(yàn)證的,適用于高達(dá) 8k 分辨率的幀尺寸和 HFR 視頻。

圖示:Vision HDL Toolbox有助于快速探索每個(gè)時(shí)鐘處理1、4或8像素

評(píng)論