Cache在POWERPC處理器板中的應用

摘要:高速緩沖存儲器Cache技術是現代處理器設計中的核心技術,文中詳細討論了Cache如何應用在POWERPC計算機板中。

關鍵詞:L1Cache;L2Cache;主存;命中率

Gibson提出高速緩存存儲器(Cache)技術后,1969年首先在IBM360/80計算機上得以實現這種技術。現在,這一技術不僅為大、中型計算機而且也為小型、微型計算機廣泛采用。解決主存與CPU的速度差異問題的技術措施有多種,設置Cache是提高存儲系統速度一個有效方法。 Cache是介于主存和CPU之間、速度數倍于主存而容量較小的快速存儲器,它的作用是使CPU能使用一個速度與CPU相當,而容量與主存相同的存儲系統。使用這種方法可使微機系統在成本增加不大的前提下性能得到較大提高。

一般的處理器中只有一級Cache,它與主存儲器構成一個兩級的存儲系統。一些高性能的處理器都采用兩級Cache,第一級Cache在CPU內部,容量很小,速度很快;第二級Cache在主板上,容量較大,速度比第一級低5倍左右。

Cache與主存儲器相比容量較小,它所保存的信息只是主存內容的一個子集。特別要注意的是,CPU與Cache之間的信息交換以“字”為單位,而Cache與主存之間的信息交換是以“塊”為單位,一個塊由若干字組成,是定長的。塊的大小通常取一個主存周期所訪問到的字節數。

當CPU試圖讀取主存一個字時,發出此字內存地址到Cache和主存,此時Cache控制邏輯依據地址進行判斷此字當前是否在Cache中。若是,此字立即遞交給CPU,否則,要用主存讀取周期把這個字從主存讀出送到CPU,與此同時把含有這個字的整個數據塊從主存讀出送到Cache中。由于程序的存儲器訪問具有局部性,當為滿足一次訪問需求而取來一數據塊時,下面的多次訪問很可能讀取此塊中的其他字。

1 局部性原理和命中率

對大量典型程序運行情況的分析結果表明,在一個較短的時間間隔內,程序對存儲器的訪問不是任意的、隨機的,而是對某一局部范圍的存儲器地址頻繁訪問,對此范圍以外地址則訪問很少,這就是程序訪問的局部性。根據程序的局部性原理,可以在主存和CPU之間設置一個高速的容量相對較小的存儲器,把正在執行的指令地址附近的一部分指令或數據從主存調入這個存儲器,供CPU在一段時間內使用。這對提高程序的運行速度有很大的作用。這個介于主存和CPU之間的高速小容量存儲器稱作高速緩沖存儲器(Cache)。CPU訪問存儲器時,首先檢查Cache,如果訪問的數據在Cache中,則CPU就能很快完成訪問,這種情況稱之命中。命中率越高,正確獲取數據的可靠性就越大。一般來說,Cache的命中率決定于Cache容量、Cache控制算法和Cache的結構。設計較好的Cache系統,命中率應存90%以上。至于沒有命中的數據,CPU只好直接從主存中獲取,同時也把它復制到Cache中,以備下次訪問。

2 Cache一致性與寫策略

在由Cache和主存儲器共同構成的Cache存儲系統中,從工作原理可知,CPU只對Cache某行信息進行修改,而主存儲器內容卻沒有修改,而其他的主控者(處理器、I/O控制器等)全由主存儲器得到過時的信息。同樣,若其他主控者修改主存儲器信息,而Cache卻沒有得到修改相應行的通知,CPU會由Cache得到過時的信息。這兩方面都會導致Cache與主存容不一致,也就是Cache的一致性問題。

為了維護Cache的一致性必須從兩方面入手,一方面涉及到處理器所采用的Cache寫策略,另一方面涉及到處理器所采用的Cache一致性協議。

2.1 寫直達法(Write—Through)

中文譯名稱為寫貫通法。顧名思義,它的做法是當Cache寫命中,Cache與主存同時發生寫修改。這種策略顯然較好地維護了Cache與主存的內容一致性,但這并不等于說全部解決一致性問題。例如在多處理器系統中各CPU都有自己的Cache,一個主存塊若在多個Cache中都有一份拷貝的話,某個CPU以寫直達法來修改它的Cache和主存時,其他Cache中的原拷貝就過時了。即使在單處理器系統中,也有I/O設備不經過Cache向主存寫入的情況。

2.2 寫回法(Write—Back)

當CPU對Cache寫命中時,只修改Cache的內容不立即寫入主存,只當此行被換出時才寫回主存。這種策略使Cache在CPU-主存之間,不僅在讀方向而且在寫方向上都起到高速緩存作用。對一Cache行的多次寫命中都在Cache中快速完成修改,只是需要替換時才寫回主存,減少了訪問主存的次數從而提高了效率。

2.3 寫一次法(Write—Once)

寫一次法是一種基于寫回法又結合了寫直達法的寫策略,即寫命中和寫未命中的處理與寫回法基本相同,只是第一次寫命中時要同時寫入主存。這種方法主要用于某些處理器的片內Cache。

L1Cache在POWERPC中的使用MPC755處理器內部Cache的執行有以下特點:

分別有兩個32-Kbyte的數據和指令Cache;

指令和數據Cache有8種設置聯系方式;

Cache的地址是物理尋址的,物理地址的標簽儲藏在Cache的地址錄中;

每一種Cache的打開與設置,可以通過設置寄存器HID0和特殊的寄存器SPR來設置。

2.4 在POWERPC處理器中設置Cache

在Memory中設置WIMG。其中,WIM改變是在頁表方式和塊方式下進行改變和設置的。

配置MMU寄存器,對MMU寄存器的塊模式進行配置。

配置HID0寄存器的Cache管理化。

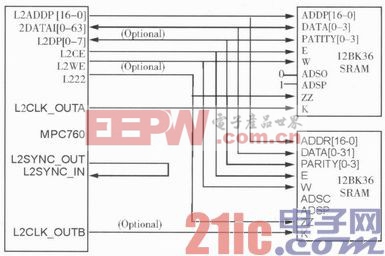

3 L2Cache在POWERPC中的使用

PPC755配置成1M的L2Cache,如下圖。

3.1 L2Cache的初始化

清除L2CR的L2E,L2CR地址為“1017”;

設置L2CR的參數;

置 L2CR[L2I]位,執行L2Cahe的global_invalidata動作;

判 L2CR[IP]位,如果為“1”,則表示global_invalidata動作完成,否則繼續判,直到變為“1”;

如果 L2CR[IP]位變為“1”,則清除L2CR[L2I]位;

使能 L2Cache,設置L2CR[L2E]位為“1”。

3.2 2Cache有效性測試

在原有程序基礎上,初始化L2Cache,使能L1Cache和L2Cache;

運行某段程序(或任務),通過設置輸出離散量的高低電平,觀察示波器波形長短,來判斷L2Cache的有效性。

4 結束語

在計算機系統中,Cache技術有效地解決了處理器和存儲器速度問不匹配問題。通過對POWERPC處理器L1Cache與L2Cache的使用,使POW ERPC處理器的性能得到了很大的提高。

存儲器相關文章:存儲器原理

評論