cache 文章 最新資訊

GPRS傳輸效能與技術(shù)

- 線網(wǎng)絡(luò)是未來網(wǎng)絡(luò)發(fā)展的趨勢(shì),除了硬設(shè)備的研發(fā),軟件的開發(fā)也是非常重要的一環(huán)。在目前的GPRS網(wǎng)絡(luò)環(huán)境里,傳輸速度以及穩(wěn)定度仍有著不足的地方,透過各種無線網(wǎng)絡(luò)最佳化技術(shù)的實(shí)作,可提供個(gè)對(duì)于目前GPRS網(wǎng)絡(luò)環(huán)境加速2~4倍的軟件解決方案,也希 望借著這個(gè)解決方案的產(chǎn)生,讓無線網(wǎng)絡(luò)的領(lǐng)域更加寬廣。

- 關(guān)鍵字: Cache GPRS IP

Cache(高速緩存)技術(shù)詳解

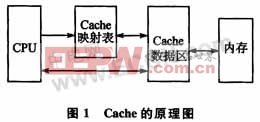

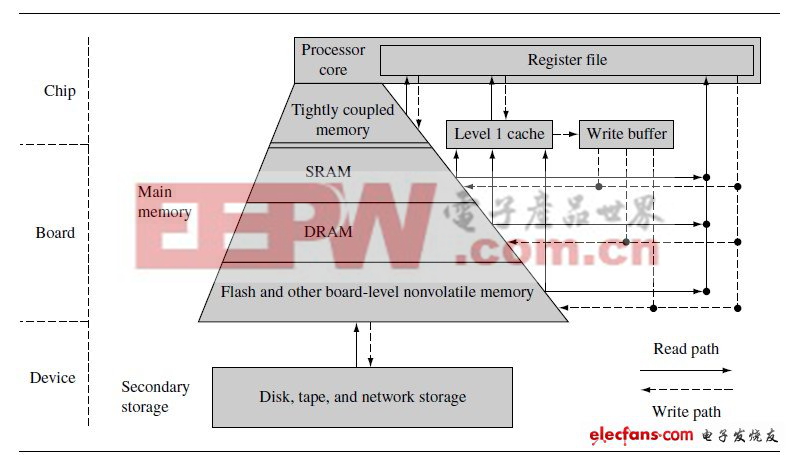

- 計(jì)算機(jī)系統(tǒng)一般都采用多級(jí)存儲(chǔ)器結(jié)構(gòu),這種多級(jí)存儲(chǔ)器的特點(diǎn)是從外存儲(chǔ)器到CPU中的寄存器逐級(jí)向上,存儲(chǔ)容量逐級(jí)減小,而存取速度逐級(jí)提高。Cache是一個(gè)速度等于或者接近上一級(jí)存儲(chǔ)器訪問速度的小容量存儲(chǔ)器,其中保存了下級(jí)存儲(chǔ)器中部分當(dāng)前所需的數(shù)據(jù),因此CPU可以直接從Cache中取得所需的數(shù)據(jù),而不必訪問下一級(jí)存儲(chǔ)器。由于Cache的速度與上一級(jí)存儲(chǔ)器相當(dāng),因此保證了系統(tǒng)效率不會(huì)降低。

- 關(guān)鍵字: cache 系統(tǒng)效率 最近最少使用算法

SPARC V8處理器斷點(diǎn)調(diào)試的設(shè)計(jì)與實(shí)現(xiàn)研究

- 以一款SPARC V8處理器為例,分析了處理器分級(jí)存儲(chǔ)系統(tǒng)中Cache和MMU對(duì)斷點(diǎn)調(diào)試實(shí)現(xiàn)的影響,提出有效的解決辦法,并成功應(yīng)用到該處理器的調(diào)試工具中。該方法也適用于其他具有Cache和MMU的處理器斷點(diǎn)調(diào)試設(shè)計(jì)。

- 關(guān)鍵字: SPARCV8處理器 cache MMU 斷點(diǎn)調(diào)試

ARM存儲(chǔ)器之:高速緩沖存儲(chǔ)器Cache

- 電子產(chǎn)品世界,為電子工程師提供全面的電子產(chǎn)品信息和行業(yè)解決方案,是電子工程師的技術(shù)中心和交流中心,是電子產(chǎn)品的市場(chǎng)中心,EEPW 20年的品牌歷史,是電子工程師的網(wǎng)絡(luò)家園

- 關(guān)鍵字: ARM 高速緩沖存儲(chǔ)器 cache

Cache在POWERPC處理器板中的應(yīng)用

- 高速緩沖存儲(chǔ)器Cache技術(shù)是現(xiàn)代處理器設(shè)計(jì)中的核心技術(shù),文中詳細(xì)討論了Cache如何應(yīng)用在POWERPC計(jì)算機(jī)板中。

- 關(guān)鍵字: POWERPC Cache 處理器 中的應(yīng)用

一種帶Cache的嵌入式CPU的設(shè)計(jì)與實(shí)現(xiàn)

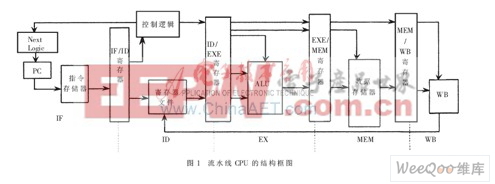

- 一種帶Cache的嵌入式CPU的設(shè)計(jì)與實(shí)現(xiàn),摘 要: 基于FPGA平臺(tái)實(shí)現(xiàn)了嵌入式RISC CPU的設(shè)計(jì)。根據(jù)項(xiàng)目要求,實(shí)現(xiàn)指令集為MIPS CPU指令集的一個(gè)子集,分析指令處理過程,構(gòu)建了嵌入式CPU的5級(jí)數(shù)據(jù)通路。分析了流水線產(chǎn)生的相關(guān)性問題,采用數(shù)據(jù)前推技術(shù)和軟件

- 關(guān)鍵字: 實(shí)現(xiàn) 設(shè)計(jì) CPU 嵌入式 Cache

Cache結(jié)構(gòu)的低功耗可重構(gòu)技術(shù)研究

- 在分析Cache性能的基礎(chǔ)上介紹了當(dāng)前低功耗Cache的設(shè)計(jì)方法,提出了一種可重構(gòu)Cache模型和動(dòng)態(tài)可重構(gòu)算法。Cache模型能夠在程序運(yùn)行過程中改變相聯(lián)度和大小,動(dòng)態(tài)可重構(gòu)算法能夠在運(yùn)行時(shí)針對(duì)不同的應(yīng)用程序?qū)芍貥?gòu)Cache進(jìn)行配置。通過對(duì)Cache的動(dòng)態(tài)配置,不僅可以提高Cache命中率,還能夠有效降低處理器的功耗。

- 關(guān)鍵字: Cache 低功耗 可重構(gòu) 技術(shù)研究

32位DSP兩級(jí)cache的結(jié)構(gòu)設(shè)計(jì)

- 采用自頂向下的流程設(shè)計(jì)了一款32位DSP的cache。該cache采用兩級(jí)結(jié)構(gòu),第一級(jí)采用哈佛結(jié)構(gòu),第二級(jí)采用普林斯頓結(jié)構(gòu)。本文詳細(xì)論述了該cache的結(jié)構(gòu)設(shè)計(jì)及采用的算法。

- 關(guān)鍵字: 結(jié)構(gòu)設(shè)計(jì) cache 兩級(jí) DSP 32位

| 共12條 1/1 1 |

cache介紹

cache ,高速緩沖存儲(chǔ)器,為一種特殊的存儲(chǔ)器子系統(tǒng),其中復(fù)制了頻繁使用的數(shù)據(jù)以利于快速訪問。存儲(chǔ)器的高速緩沖存儲(chǔ)器存儲(chǔ)了頻繁訪問的 RAM 位置的內(nèi)容及這些數(shù)據(jù)項(xiàng)的存儲(chǔ)地址。當(dāng)處理器引用存儲(chǔ)器中的某地址時(shí),高速緩沖存儲(chǔ)器便檢查是否存有該地址。如果存有該地址,則將數(shù)據(jù)返回處理器;如果沒有保存該地址,則進(jìn)行常規(guī)的存儲(chǔ)器訪問。因?yàn)楦咚倬彌_存儲(chǔ)器總是比主RAM 存儲(chǔ)器速度快,所以當(dāng) RAM 的訪問 [ 查看詳細(xì) ]

相關(guān)主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司