技術革命!主流芯片架構正在發生重大變化?

主流的芯片制造商和系統供應商都在改變方向,引發了一場架構創新大賽,創新涉及從存儲器中讀取和寫入數據的方式、數據管理和處理方式以及單個芯片上的各個元素的結合方式等。雖然工藝節點尺寸仍在繼續縮減,但是沒有人寄希望于工藝的進步可以跟得上傳感器數據的爆炸性增長以及芯片間數據流量增加的步伐。

在這些創新中, 新型處理器架構專注于研究每個時鐘周期內處理更多數據的方法,有時犧牲部分精度,或者根據應用類型提高特定操作的優先級;

正在開發的新存儲器架構改變了數據存儲、讀取、寫入和訪問的方式;

更有針對性的處理元素散布在系統周圍,更加靠近內存。系統不再依賴于最適合應用的單個主處理器,而是根據數據類型和應用選擇不同的加速器;

通過人工智能技術,將不同的數據類型融合在一起,形成多種模式,有效地提高了數據密度,同時最大限度地減少不同數據類型之間的差異;

封裝組合形式成為架構設計的核心之一,越來越關注修改設計的難易。

“有一些趨勢導致人們試圖充分挖掘已有方案的潛力。” Rambus的杰出發明家Steven Woo說,“在數據中心上,你希望硬件和軟件能夠發揮盡可能多的作用,這是數據中心重新思考其經濟成本的方式。啟用一種新功能的成本非常高,但是瓶頸正在日益凸顯,所以我們看到更多專用芯片和提高計算效率的方法不斷涌現,如果可以減少數據在內存和I/O上來回傳輸的次數,將會產生很大的影響。”

這些變化在邊緣節點上更加明顯,此外,系統供應商突然意識到有數百億臺設備不斷地產生天量數據,而這些數據無法全部發送到云端進行處理。在邊緣節點上處理這些數據對節點自身帶來了挑戰,它們需要在不顯著改變功耗預算的情況下大幅提高性能。

英偉達的Tesla產品家族首席平臺架構師Robert Ober說:“人們把重點放在降低精度上,邊緣節點性能的提升不僅僅體現在更多計算周期上。它需要在內存中放入更多數據,比如您可以使用16位指令格式。 所以,解決方案不是為了提高處理效率而在緩存中存儲更多內容。從統計上看,不同精度的計算結果應該是一致的。”

Ober預測,在可預見的未來,通過一系列架構優化應該可以每隔幾年就將處理速度提高一倍。“我們將見證這些改變,”他說。“為了實現這一目標,我們需要在三個層面實現突破。第一是計算,第二是內存,在某些模型中,計算更關鍵,而在其它模型中內存更關鍵。第三是主處理器帶寬和I/O帶寬,我們需要在優化存儲和網絡方面做很多工作。”

其中一些變化已經發生。在Hot Chips 2018會議上的演講中,三星奧斯汀研發部門的首席架構師 Jeff Rupley指出了該公司M3處理器的幾個主要架構變化。其中一個是每個周期處理更多的指令,相比于之前M2處理的四條指令/周期,M3為6條。還包括以若干神經網絡取代預取搜索,改善了分支預測,以及將指令隊列深度加倍。

從另一個角度來看,這些變化也改變了從制造工藝到前端架構/設計和后端封裝的協同創新關系。雖然制造工藝仍在不斷創新,但是每次新節點只能帶來15%到20%的性能和功耗改善,顯然不足以跟上數據的增長步伐。

“變化正以指數速度發生,”Xilinx總裁兼首席執行官Victor Peng在Hot Chips的演講中表示。 “現在每年將產生10個zettabytes [1021字節]的數據,其中大部分是非結構化數據。”

存儲器領域的新方案

處理這么多數據需要重新思考系統中的每個元素,從數據的處理方式到存儲方式都需要重新設計。

“業界已經進行了多次嘗試,以創建新的內存架構,”eSilicon EMEA創新高級主管CarlosMaciàn說。“當前內存的瓶頸在于你需要讀取出一整行,然后再在其中選擇一位。一種新方法是構建可以從左到右、從上到下讀取的內存。您還可以更進一步,將計算能力部署到不同的內存中。”

還可以改變內存的讀取方式、處理單元的位置和類型,以及使用人工智能技術優化不同數據在整個系統中存儲、處理、傳輸的優先級。

“在稀疏數據中,我們一次只能從字節陣列讀取一個字節的數據,在其它類型應用中,也可以在同樣的字節陣列中一次讀取八個連續數據,而不會消耗與我們不感興趣的其它字節或字節陣列相關的能耗,”Cadence產品營銷部門總監Marc Greenberg說。 “未來的新型內存可能更適合處理這類事情。比如我們看一下HBM2的架構,HBM2硅片堆棧被安排到16個64位的虛擬通道中,我們從任何一次對任何虛擬通道的訪問中都能得到4個連續的64位字。因此,有可能構建可水平寫入的1,024位寬的數據陣列,一次只讀取4個64位字。”

內存是馮諾依曼架構的核心組件之一,也正在成為架構創新的最大試驗田之一。AMD的客戶端產品首席架構師Dan Bouvier表示:“現有架構的一個大報應就是虛擬內存系統,它迫使你以更加不自然的方式移動數據。你需要執行一次又一次轉換。如果您可以消除DRAM中的分區沖突,您可以獲得更高效的數據流動。分立GPU可以在90%的效率區間運行DRAM,效率非常高。但是,如果你可以獲得串行的數據傳輸,你也可以在APU和CPU上在80%到85%的效率區間內運行DRAM。”

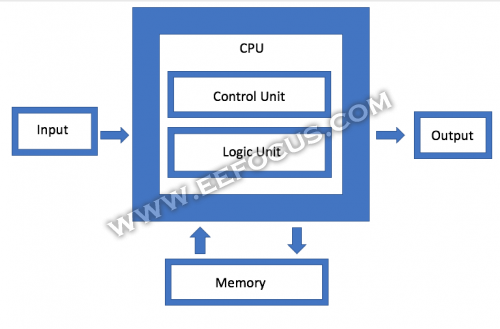

馮諾依曼架構

IBM正在開發一種不同類型的內存架構,它本質上是磁盤條帶化技術的現代版本。磁盤條帶化技術將數據不再局限在單個磁盤上,同樣,IBM新型內存架構的目標是利用被其系統硬件架構師Jeff Stuecheli稱為連接技術的“瑞士軍刀”的連接器技術,混合和匹配不同類型的數據。

“CPU變成了一個位于高性能信號接口中間的東西,”Stuecheli說。“如果你修改微體系結構,不用提高頻率,內核就可以在每個周期內做更多的事情。”

為了確保這些體系架構能夠處理越來越龐大的數據,連接性和吞吐能力變得越來越重要。 “現在最大的瓶頸在于數據傳輸,”Rambus的Woo說。 “半導體行業在提高計算性能方面做得非常出色。 但是,如果您把大量時間用在等待數據或特定的數據模式上,效率依然無法提高。必須更快地運行內存。因此,如果你看看DRAM和非易失性存儲器就會發現,它們的性能實際上取決于數據傳輸模式。如果您能夠將數據串起來,就可以在內存中獲得非常高的效率。但是如果你的數據在空間上隨機分布,效率就會降低。無論你怎么做,隨著數據量的增加,你必須保證能夠更快地完成所有這些數據傳輸。”

評論