基于網(wǎng)絡(luò)編碼的多信源組播通信系統(tǒng),包括源代碼,原理圖等 (三)

③decode_control_sm

該模塊的功能是按照輪詢策略,控制decoder解碼儲(chǔ)存在DRAM中的數(shù)據(jù)包。通過查詢CAM中的數(shù)據(jù)包的存儲(chǔ)地址,將查詢到的地址輸出給DRAM讀寫控制模塊,從而找到解碼所需要的數(shù)據(jù),同時(shí)將要查詢的數(shù)據(jù)包的信源號(hào)和代的編號(hào)發(fā)送給解碼模塊。若不能查找到解碼因子,則將信號(hào)Pkt_not_find置為有效電平,通知decoder無法解碼,同時(shí)將狀態(tài)轉(zhuǎn)到解碼下一個(gè)數(shù)據(jù)包的狀態(tài)上。在開始查找CAM時(shí),要等待儲(chǔ)存一定數(shù)量的數(shù)據(jù)包,在我們的系統(tǒng)里面,暫定為32。

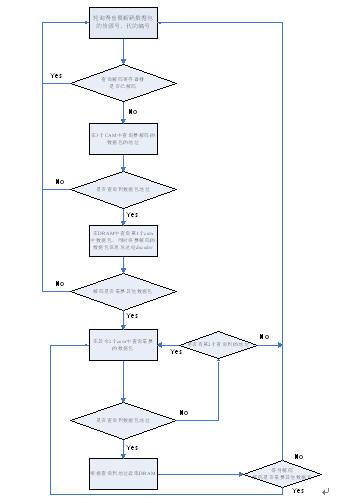

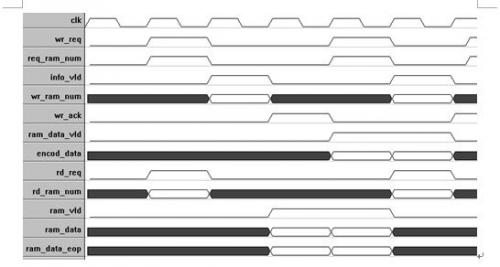

狀態(tài)機(jī)處理控制流程如圖3.4-13:

圖3.4-13:decode_control_sm狀態(tài)機(jī)及數(shù)據(jù)處理流程

6、decoder

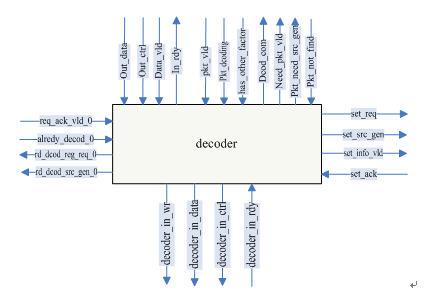

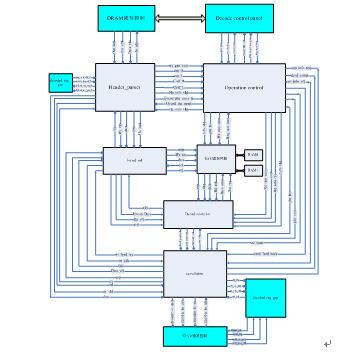

decoder是整個(gè)解碼路由器的核心之一,它的主要功能是接收來自DRAM的編碼后的IP數(shù)據(jù)包,在decode_control_panel模塊的控制下對(duì)數(shù)據(jù)包進(jìn)行解碼,它包括多個(gè)小模塊,其整體圖和內(nèi)部結(jié)構(gòu)圖如3.4-14和3.4-15所示:

圖3.4-14 decoder整體結(jié)構(gòu)圖

圖3.4-15:decoder內(nèi)部結(jié)構(gòu)圖

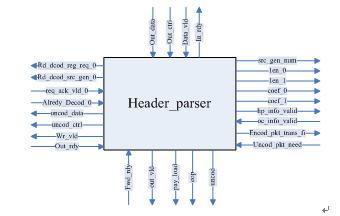

① header_parser

分析接收到的數(shù)據(jù)包,如果已經(jīng)被編碼,根據(jù)包頭提取信源號(hào)、代號(hào)、長(zhǎng)度和系數(shù)給運(yùn)算控制模塊,如果沒有被編碼,則查詢解碼標(biāo)志寄存器,如果已經(jīng)解碼并儲(chǔ)存在二級(jí)緩存中,則該數(shù)據(jù)包只是一個(gè)解碼因子,把數(shù)據(jù)發(fā)送到fwd_sel,若沒有解碼,則同時(shí)發(fā)送到capsulation和forward sel。如果數(shù)據(jù)是編碼后的數(shù)據(jù)包,則將數(shù)據(jù)包去掉包頭后將數(shù)據(jù)發(fā)送給forward sel模塊。當(dāng)發(fā)送到最后的64位數(shù)據(jù)時(shí),eop信號(hào)有效,指明是數(shù)據(jù)包的最后有效字節(jié)。

下圖所示為輸入輸出接口圖3.4-16:

圖3.4-16:header_parser模塊圖

其輸入輸出端口列表如下:

信號(hào)名稱 | 位寬bits | I/O | 描述 |

in_rdy | 1 | O | 數(shù)據(jù)輸出輸入允許信號(hào) |

out_data | 64 | I | 輸入的數(shù)據(jù)包的data_bus |

out_ctrl | 8 | I | 輸入數(shù)據(jù)包的ctrl_bus |

data_vld | 1 | I | 輸入數(shù)據(jù)有效 |

rd_dcod_reg_req_0 | 1 | O | 讀取解碼標(biāo)志位請(qǐng)求 |

rd_dcod_src_gen_0 | 12 | O | 要讀取的數(shù)據(jù)包的信源號(hào)和代編號(hào) |

req_ack_vld_0 | 1 | I | 輸入有效 |

alredy_decod_0 | 1 | I | 解碼標(biāo)志(“1”代表已經(jīng)解碼,“0”代表未解碼) |

Uncod_data | 64 | O | 未編碼數(shù)據(jù)包的數(shù)據(jù)總線 |

Uncod_ctrl | 8 | O | 未編碼數(shù)據(jù)包的控制總線 |

Wr_vld | 1 | O | 寫capsulation數(shù)據(jù)有效 |

Out_rdy | 1 | I | 輸出capsulation允許信號(hào) |

fwd_rdy | 1 | I | 輸出fwd_sel允許信號(hào) |

out_vld | 1 | O | 輸出fwd_sel有效 |

pay_load | 64 | O | 輸出fwd_sel數(shù)據(jù)(不含包頭) |

eop | 4 | O | 最后指示一個(gè)有效字節(jié)的指示 |

uncod | 1 | O | 指明輸出的數(shù)據(jù)包是否編碼 |

src_gen_num | 12 | O | Decoder接收到的數(shù)據(jù)包的信源號(hào)和代的編號(hào) |

len_0 | 16 | O | 被編碼的第一個(gè)數(shù)據(jù)包的有效載荷的長(zhǎng)度 |

len_1 | 16 | O | 被編碼的第二個(gè)數(shù)據(jù)包的有效載荷的長(zhǎng)度 |

coef_0 | 8 | O | 被編碼的第一個(gè)數(shù)據(jù)包的編碼系數(shù) |

coef_1 | 8 | O | 被編碼的第二個(gè)數(shù)據(jù)包的編碼系數(shù) |

hp_info_vld | 1 | O | 輸出信息有效 |

encod_pkt_trans_fi | 1 | O | 編碼數(shù)據(jù)包傳輸完畢標(biāo)志 |

oc_info_vld | 1 | I | 解碼控制輸入信息有效 |

uncod_pkt_need | 1 | I | 未編碼的數(shù)據(jù)包是/否解碼因子(1=是,0=否) |

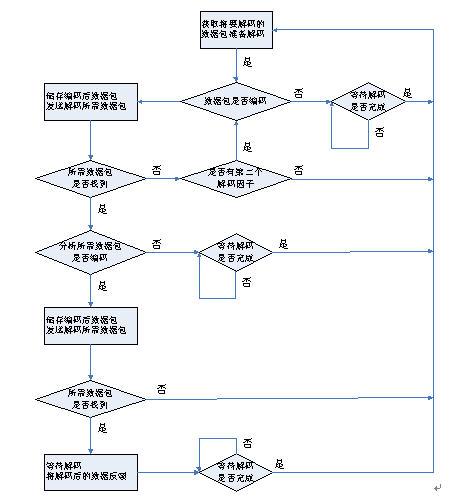

圖3.4-17所示為狀態(tài)機(jī)處理流程:

圖3.4-17:header_parser狀態(tài)機(jī)處理流程

② forwd_sel

該模塊功能主要是轉(zhuǎn)發(fā)數(shù)據(jù)包:接收來自header_parser的數(shù)據(jù)包,若uncod=0,則表明數(shù)據(jù)包是編碼后數(shù)據(jù)包,將已經(jīng)編碼后的數(shù)據(jù)包的載荷轉(zhuǎn)換為72bits后,將數(shù)據(jù)發(fā)送到RAM讀寫控制器,否則發(fā)送到decod_operation。當(dāng)有反饋輸入請(qǐng)求時(shí),若輸出到decod_operation 的數(shù)據(jù)線空閑時(shí),將反饋數(shù)據(jù)發(fā)送到decod_operation。

本模塊的端口列表如下:

信號(hào)名稱 | 位寬bits | I/O | 信號(hào)描述 |

fwd_rdy | 1 | O | 輸入fwd_sel允許信號(hào) |

out_vld | 1 | I | 輸入fwd_sel有效 |

pay_load | 64 | I | 輸入fwd_sel數(shù)據(jù)總線(不含包頭) |

eop | 4 | I | 最后指示一個(gè)有效字節(jié)的指示 |

uncod | 1 | I | 指明輸出的數(shù)據(jù)包是否編碼 |

wr_req | 1 | O | 寫RAM請(qǐng)求 |

encod_data | 72 | O | 寫RAM的數(shù)據(jù)總線 |

ram_data_vld | 1 | O | 數(shù)據(jù)有效 |

encod_data_eop | 4 | O | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

wr_ack | 1 | I | 寫RAM響應(yīng) |

uncod_data_vld | 1 | O | 輸出至dcod_operation的數(shù)據(jù)有效 |

uncod_data_factor | 64 | O | 輸出至dcod_operation的數(shù)據(jù)總線 |

uncod_data_eop | 4 | O | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

dcod_rdy | 1 | I | 輸出至dcod_operation允許信號(hào) |

fd_back_ack | 1 | O | 接受反饋響應(yīng) |

fd_back_vld | 1 | I | 反饋數(shù)據(jù)有效標(biāo)志 |

fd_back_req | 1 | I | 反饋請(qǐng)求 |

fd_back_data | 64 | I | 反饋數(shù)據(jù)總線 |

fd_back_data_eop | 4 | I | 反饋數(shù)據(jù)結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

③ RAM讀寫控制器

在寫數(shù)據(jù)時(shí),先從運(yùn)算控制模塊中得出要儲(chǔ)存的RAM號(hào),接著RAM讀寫控制器將從收到forward sel 模塊收到的數(shù)據(jù)存到片內(nèi)RAM里面去。在讀數(shù)據(jù)時(shí),根據(jù)dcod_operation模塊提供的ram號(hào),從相應(yīng)的ram中讀取數(shù)據(jù),由于使用的是雙端口ram,因此讀寫可以同時(shí)進(jìn)行。模塊信號(hào)列表如下:

信號(hào)名稱 | 位寬bits | I/O | 信號(hào)描述 |

wr_req | 1 | I | 寫RAM請(qǐng)求 |

encod_data | 72 | I | 寫RAM的數(shù)據(jù)總線 |

ram_data_vld | 1 | I | 數(shù)據(jù)有效 |

encod_data_eop | 4 | I | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

wr_ack | 1 | O | 寫RAM響應(yīng) |

wr_ram_num | 2 | I | 要寫入的RAM號(hào) |

info_vld | 1 | I | 數(shù)據(jù)有效標(biāo)志 |

req_ram_num | 1 | O | 讀RAM號(hào)請(qǐng)求 |

rd_ram_num | 2 | I | 需要讀取數(shù)據(jù)的RAM號(hào) |

rd_req | 1 | I | 讀RAM請(qǐng)求 |

ram_data_eop | 4 | O | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

ram_data | 72 | O | 讀RAM的數(shù)據(jù)總線 |

ram_vld | 1 | O | 讀RAM數(shù)據(jù)有效 |

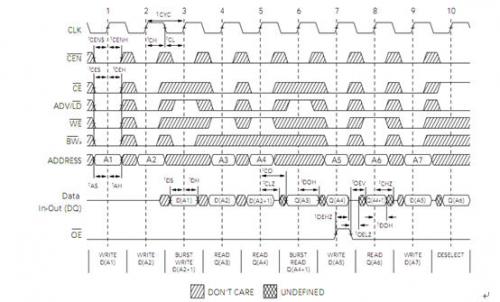

RAM讀寫時(shí)序圖如圖3.4-18:

圖3.4-18:RAM讀寫時(shí)序

每個(gè)RAM由雙端口block RAM組成,位寬為72位,深度為180,因此讀寫的地址位寬均為8位。由于RAM的讀寫控制時(shí)序是固定的,所以在此不再贅述。

④ operation_control

運(yùn)算控制(operation_control)是decoder模塊的控制核心,它和decode_control_panel配合,完成對(duì)編碼數(shù)據(jù)包的解碼。

輸入輸出信號(hào)列表:

信號(hào)名稱 | 位寬bits | I/O | 信號(hào)描述 |

Pkt_vld | 1 | I | 要解碼的數(shù)據(jù)包輸出有效標(biāo)志 |

Pkt_decoding | 12 | I | 正在解碼的數(shù)據(jù)包的信源號(hào)、代編號(hào) |

Decod_com | 1 | O | 數(shù)據(jù)包解碼完成標(biāo)志 |

has_other_factor | 1 | I | 有另外一個(gè)解碼因子 |

Pkt_not_find | 1 | I | 所需要解碼數(shù)據(jù)包未找到 |

pkt_need_src_gen | 12 | O | 解碼需要的數(shù)據(jù)包 |

need_pkt_vld | 1 | O | 所需數(shù)據(jù)包有效 |

src_gen_num | 12 | I | Decoder接收到的數(shù)據(jù)包的信源號(hào)和代的編號(hào) |

len_0 | 16 | I | 被編碼的第一個(gè)數(shù)據(jù)包的有效載荷的長(zhǎng)度 |

len_1 | 16 | I | 被編碼的第二個(gè)數(shù)據(jù)包的有效載荷的長(zhǎng)度 |

coef_0 | 8 | I | 被編碼的第一個(gè)數(shù)據(jù)包的編碼系數(shù) |

coef_1 | 8 | I | 被編碼的第二個(gè)數(shù)據(jù)包的編碼系數(shù) |

hp_info_vld | 1 | I | 輸入信息有效 |

encod_pkt_trans_fi | 1 | I | 編碼數(shù)據(jù)包傳輸完畢標(biāo)志 |

oc_info_vld | 1 | O | 解碼控制輸出信息有效 |

uncod_pkt_need | 1 | O | 未編碼的數(shù)據(jù)包是/否解碼因子(1=是,0=否) |

wr_ram_num | 2 | O | 要寫入的RAM號(hào) |

info_vld | 1 | O | 數(shù)據(jù)有效標(biāo)志 |

req_ram_num | 1 | I | 讀RAM號(hào)請(qǐng)求 |

rd_info_req | 1 | I | 讀取解碼信息請(qǐng)求 |

dcod_info_vld | 1 | O | 解碼信息有效 |

ram_num | 2 | O | 解碼數(shù)據(jù)包的所存儲(chǔ)的RAM號(hào) |

coef_mut | 8 | O | 乘法系數(shù) |

coef_div | 8 | O | 除法系數(shù) |

cap_info_req | 1 | I | 封裝信息請(qǐng)求 |

dcod_comp | 1 | I | 解碼封裝完成 |

cap_info_vld | 1 | O | 封裝信息有效 |

need_feed_back | 1 | O | 需要反饋 |

pkt_len | 16 | O | 數(shù)據(jù)包長(zhǎng)度 |

src_num | 4 | O | 數(shù)據(jù)包的信源號(hào) |

gen_num | 8 | O | 數(shù)據(jù)報(bào)的代編號(hào) |

Operation_control模塊的主要功能是:接收header_parser發(fā)送過來的數(shù)據(jù),通過計(jì)算和比較后與decode control panel通信,告訴decode control panel解碼所需要的數(shù)據(jù)包和解碼完成標(biāo)志;給RAM讀寫給出RAM號(hào)(即存儲(chǔ)在哪個(gè)RAM中);給decode operation模塊提供解碼所需要的系數(shù)和RAM號(hào);給capsulation模塊提供源IP和是否需要反饋數(shù)據(jù)的命令,其控制狀態(tài)如圖3.4-19下:

圖3.4-19:Operation_control狀態(tài)機(jī)處理流程

⑤ decode operation

decode operation是解碼運(yùn)算模塊,它將來自fwd_sel模塊的未編碼的數(shù)據(jù)和來自RAM的編碼數(shù)據(jù)完成減法和除法運(yùn)算,還原被編碼的數(shù)據(jù)。解碼后將數(shù)據(jù)總線的位寬恢復(fù)為64bits。解碼運(yùn)算模塊的端口列表如下:

信號(hào)名稱 | 位寬bits | I/O | 信號(hào)描述 |

dcod_payload | 64 | O | 解碼后的數(shù)據(jù)包的有效載荷 |

end_payload | 4 | O | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

payload_vld | 1 | O | 輸出數(shù)據(jù)有效 |

wr_rdy | 1 | I | 輸出數(shù)據(jù)允許信號(hào) |

uncod_data_vld | 1 | I | 輸入至dcod_operation的數(shù)據(jù)有效 |

uncod_data_factor | 64 | I | 輸入至dcod_operation的數(shù)據(jù)總線 |

uncod_data_eop | 4 | I | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

dcod_rdy | 1 | O | 輸入至dcod_operation允許信號(hào) |

rd_ram_num | 2 | O | 需要讀取數(shù)據(jù)的RAM號(hào) |

rd_req | 1 | O | 讀RAM請(qǐng)求 |

ram_data_eop | 4 | I | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

ram_data | 72 | I | 讀RAM的數(shù)據(jù)總線 |

ram_vld | 1 | I | 讀RAM數(shù)據(jù)有效 |

rd_info_req | 1 | O | 讀取解碼信息請(qǐng)求 |

dcod_info_vld | 1 | I | 解碼信息有效 |

ram_num | 2 | I | 解碼數(shù)據(jù)包的所存儲(chǔ)的RAM號(hào) |

coef_mut | 8 | I | 乘法系數(shù) |

coef_div | 8 | I | 除法系數(shù) |

為了快速完成解碼運(yùn)算,我們?cè)诖瞬扇〔⑿谐ǖ姆椒ㄊ怪芸焖俳獯a,解碼運(yùn)算的算法圖如圖3.4-20:

圖3.4-20 decoder_operation內(nèi)部的并行除法

⑥ capsulation

Capsulation是解碼運(yùn)算的最后一個(gè)模塊,其主要功能是封裝解碼后的數(shù)據(jù)包。其主要任務(wù)是:(1)接收來自decode operation和header_parser的數(shù)據(jù);(2)將來自header_parser的未編碼的數(shù)據(jù)包去掉NCP包頭;(3)計(jì)算新的包頭校驗(yàn)和,更新TTL;(4)置位解碼標(biāo)志寄存器;(5)將來自decode operation模塊的數(shù)據(jù),先向運(yùn)算控制模塊詢問是否要反饋,若需要,則將數(shù)據(jù)反饋至forward_sel模塊;(6)恢復(fù)IP數(shù)據(jù)包頭;(7)將IP包頭和有效載荷封裝好,并恢復(fù)ctrl_bus和module header,將其一起同步發(fā)送出去。

端口信號(hào)列表如下:

信號(hào)名稱 | 位寬bits | I/O | 信號(hào)描述 |

decoder_in_rdy | 1 | I | 輸出至SRAM允許信號(hào) |

decoder_in_wr | 1 | O | 輸出有效 |

decoder_in_data | 64 | O | 輸出至SRAM數(shù)據(jù)總線 |

decoder_in_ctrl | 8 | O | 輸出至SRAM控制總線 |

set_req | 1 | O | 置位請(qǐng)求 |

set_src_gen | 12 | O | 需要置位的數(shù)據(jù)包(表示已經(jīng)解碼完畢) |

set_info_vld | 1 | O | 置位信息有效 |

set_ack | 1 | I | 置位請(qǐng)求響應(yīng) |

cap_info_req | 1 | O | 封裝信息請(qǐng)求 |

dcod_comp | 1 | O | 解碼封裝完成 |

cap_info_vld | 1 | I | 封裝信息有效 |

need_feed_back | 1 | I | 需要反饋 |

pkt_len | 16 | I | 數(shù)據(jù)包長(zhǎng)度 |

src_num | 4 | I | 數(shù)據(jù)包的信源號(hào) |

gen_num | 8 | I | 數(shù)據(jù)報(bào)的代編號(hào) |

dcod_payload | 64 | I | 解碼后的數(shù)據(jù)包的有效載荷 |

end_payload | 4 | I | 數(shù)據(jù)包結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

payload_vld | 1 | I | 輸入數(shù)據(jù)有效 |

wr_rdy | 1 | O | 輸入數(shù)據(jù)允許信號(hào) |

fd_back_ack | 1 | I | 接受反饋響應(yīng) |

fd_back_vld | 1 | O | 反饋數(shù)據(jù)有效標(biāo)志 |

fd_back_req | 1 | O | 反饋請(qǐng)求 |

fd_back_data | 64 | O | 反饋數(shù)據(jù)總線 |

fd_back_data_eop | 4 | O | 反饋數(shù)據(jù)結(jié)束標(biāo)志,指明最后一個(gè)有效字節(jié) |

Uncod_data | 64 | I | 未編碼數(shù)據(jù)包的數(shù)據(jù)總線 |

Uncod_ctrl | 8 | I | 未編碼數(shù)據(jù)包的控制總線 |

Wr_vld | 1 | I | 寫capsulation數(shù)據(jù)有效 |

Out_rdy | 1 | O | 輸入數(shù)據(jù)包允許信號(hào) |

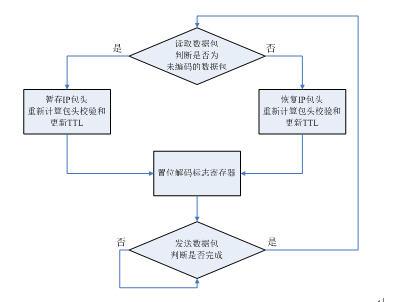

封裝過程中的狀態(tài)轉(zhuǎn)換圖如圖3.4-21:

圖3.4-21capsulation封裝包頭流程圖

7、SRAM讀寫控制器

SRAM讀寫控制的作用是:①將capsulation模塊來的數(shù)據(jù)寫入SRAM中,寫入時(shí)按照代的大小和信源號(hào)寫入block中。SRAM按照地址分為3個(gè)區(qū)域,每個(gè)區(qū)域存儲(chǔ)對(duì)應(yīng)由一個(gè)信源。每個(gè)區(qū)域分為256個(gè)block,每個(gè)block深度是400,寬度為36bits,可以存儲(chǔ)1800字節(jié)的數(shù)據(jù)(即至少可容納一個(gè)正常大小的IP數(shù)據(jù)包)。②讀取數(shù)據(jù)時(shí)按照block逐個(gè)讀取,讀取后的數(shù)據(jù)直接發(fā)送至output_arbiter。在每發(fā)送完一個(gè)數(shù)據(jù)包后,對(duì)解碼標(biāo)志寄存器復(fù)位。

SRAM讀寫控制器的端口列表如下:

信號(hào)名稱 | 位寬bits | I/O | 信號(hào)描述 |

decoder_in_rdy | 1 | O | 寫SRAM控制器允許信號(hào) |

decoder_in_wr | 1 | I | 輸入有效 |

decoder_in_data | 64 | I | 輸入至SRAM控制器數(shù)據(jù)總線 |

decoder_in_ctrl | 8 | I | 輸入至SRAM控制器控制總線 |

reset_req | 1 | O | 復(fù)位請(qǐng)求 |

reset_src_gen | 12 | O | 需要復(fù)位的數(shù)據(jù)包(表示解碼后已發(fā)送完畢) |

reset_info_vld | 1 | O | 復(fù)位信息有效 |

reset_ack | 1 | I | 復(fù)位請(qǐng)求響應(yīng) |

dcod_data_0 | 64 | O | 輸出的IP數(shù)據(jù)包的數(shù)據(jù)總線 |

dcod_ctrl_0 | 8 | O | 輸出的IP數(shù)據(jù)包的控制總線 |

wr_vld_0 | 1 | O | 輸出有效 |

wr_rdy_0 | 1 | I | 發(fā)送數(shù)據(jù)允許標(biāo)志 |

sram_addr | 19 | O | Sram讀/寫地址 |

sram_we | 1 | O | Sram寫使能 |

sram_bw | 4 | O | SRAM寫入控制信號(hào) |

sram_wr_data | 36 | O | SRAM寫數(shù)據(jù)總線 |

sram_rd_data | 36 | I | SRAM讀數(shù)據(jù)總線 |

sram_tri_en | 1 | O | SRAM寫三態(tài)控制 |

SRAM的讀寫時(shí)序如圖3.4-22:

圖3.4-22 SRAM讀寫時(shí)序

評(píng)論