基于網(wǎng)絡(luò)編碼的多信源組播通信系統(tǒng),包括源代碼,原理圖等 (三)

3.4 解碼路由器詳細(xì)設(shè)計(jì)方案

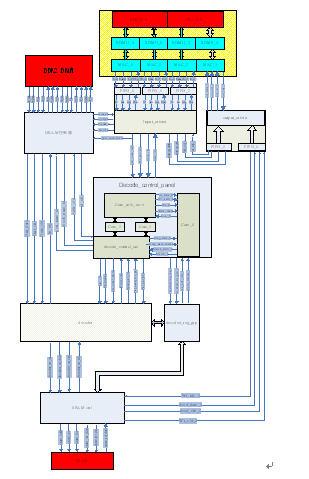

3.4.1 解碼路由器系統(tǒng)整體模塊圖

如下圖3.4-1所示,為解碼路由器的整體模塊圖

3.4-1 解碼路由器系統(tǒng)整體模塊圖

3.4.2系統(tǒng)中各單元模塊的功能與時(shí)序

1、Input_arbiter:采用輪詢策略,當(dāng)fifo非空時(shí)從fifo接收數(shù)據(jù),根據(jù)mac header判斷數(shù)據(jù)是否為IP數(shù)據(jù)包,若是,則將數(shù)據(jù)發(fā)送到DRAM讀寫控制模塊,同時(shí)將信源號(hào)、代編號(hào)發(fā)送到CAM讀寫控制模塊。

可用一個(gè)兩狀態(tài)的狀態(tài)機(jī)實(shí)現(xiàn):即輪詢判斷輸入和數(shù)據(jù)輸出:在FIFO非空時(shí)讀數(shù)據(jù),并根據(jù)數(shù)據(jù)包的類型發(fā)送到DRAM讀寫控制器或output fifo中,若是IP數(shù)據(jù)包,同時(shí)將信源號(hào)、代編號(hào)發(fā)送給CAM讀寫控制。

主要信號(hào)列表:

信號(hào)名稱 | 位寬 bit | I/O | 描述 |

Wr_vld_arb | 1 | 寫DRAM控制器有效 | |

Out_data_0 | 64 | 輸出至DRAM的data | |

Out_ctrl_0 | 8 | 輸出至DRAM德ctrl | |

Src_gen_seq | 24 | 信源號(hào)、代的編號(hào) | |

Cam_vld | 1 | 寫CAM控制器有效 | |

Port_num_dram | 2 | 數(shù)據(jù)的接收端口號(hào) | |

Out_data_1 | 64 | 輸出至output arbiter的data | |

Out_ctrl_1 | 8 | 輸出至output arbiter的ctrl | |

Wr_vld_1 | 1 | 輸出至output arbiter信號(hào)有效 |

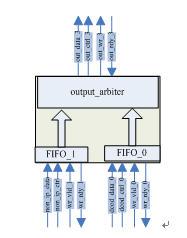

2、output_arbiter

圖3.4-2 output_arbiter結(jié)構(gòu)圖

本模塊的結(jié)構(gòu)如圖3.4-2所示,由兩個(gè)輸入fifo和一個(gè)輸出仲裁器組成,兩個(gè)fifo緩存來(lái)自SRAM和input_arbiter的數(shù)據(jù)包,Output_arbiter的作用是將解碼后的數(shù)據(jù)發(fā)送到MAC層。由于對(duì)于非IP數(shù)據(jù)包我們并沒(méi)有對(duì)其進(jìn)行編碼,所以在解碼路由器中由input_arbiter判斷后直接輸出output_arbiter;對(duì)于編碼后的IP數(shù)據(jù)包,在解碼后先暫存到SRAM中,再發(fā)送出去。本模塊就是輪流判斷并接收來(lái)自SRAM和input_arbiter的數(shù)據(jù),并將數(shù)據(jù)包發(fā)送到MAC層。

輸入輸出信號(hào)列表:

信號(hào)名稱 | 位寬bits | I/O | 描述 |

out_data_3 | 64 | O | 輸出至MAC層的數(shù)據(jù)總線 |

out_ctrl_3 | 8 | O | 輸出至MAC層的控制總線 |

out_wr_3 | 1 | O | 輸出有效 |

out_rdy_3 | 1 | I | MAC層空閑標(biāo)志 |

dcod_data_0 | 64 | I | 已經(jīng)解碼的IP數(shù)據(jù)包的數(shù)據(jù)總線 |

dcod_ctrl_0 | 8 | I | 已經(jīng)解碼的IP數(shù)據(jù)包的控制總線 |

wr_vld_0 | 1 | I | 寫有效 |

wr_rdy_0 | 1 | O | 接收數(shù)據(jù)空閑標(biāo)志 |

non_ip_data | 64 | I | 非IP數(shù)據(jù)包數(shù)據(jù)總線 |

non_ip_ctrl | 8 | I | 非IP數(shù)據(jù)包控制總線 |

wr_vld_1 | 1 | I | 寫有效 |

wr_rdy_1 | 1 | O | 接收數(shù)據(jù)空閑標(biāo)志 |

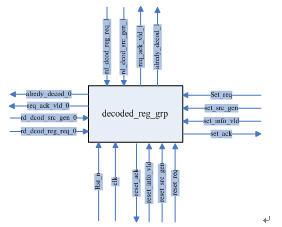

3、decoded_reg_grp

本模塊分別與decode_control_panel,decoder和SRAM_contrl相連接,主要作用是記錄信源的某代數(shù)據(jù)包是否已經(jīng)解碼,并將相應(yīng)的解碼信息輸出給其他模塊,模塊結(jié)構(gòu)如圖3.4-3:

圖3.4-3:decoded_reg_grp模塊圖

端口列表:

信號(hào)名稱 | 位寬bits | I/O | 描述 |

rd_dcod_reg_req_0 | 1 | I | 讀取解碼標(biāo)志位請(qǐng)求 |

rd_dcod_src_gen_0 | 12 | I | 要讀取的數(shù)據(jù)包的信源號(hào)和代編號(hào) |

req_ack_vld_0 | 1 | O | 輸出有效 |

alredy_decod_0 | 1 | O | 解碼標(biāo)志(“1”代表已經(jīng)解碼,“0”代表未解碼) |

rd_dcod_reg_req_1 | 1 | I | 讀取解碼標(biāo)志位請(qǐng)求 |

rd_dcod_src_gen_1 | 12 | I | 要讀取的數(shù)據(jù)包的信源號(hào)和代編號(hào) |

req_ack_vld_1 | 1 | O | 輸出有效 |

alredy_decod_1 | 1 | O | 解碼標(biāo)志(為1時(shí)代表已經(jīng)解碼,為0時(shí)未解碼) |

set_req | 1 | I | 置位請(qǐng)求 |

set_src_gen | 12 | I | 需要置位的數(shù)據(jù)包(表示已經(jīng)解碼完畢) |

set_info_vld | 1 | I | 置位信息有效 |

set_ack | 1 | O | 置位請(qǐng)求響應(yīng) |

reset_req | 1 | I | 復(fù)位請(qǐng)求 |

reset_src_gen | 12 | I | 需要復(fù)位的數(shù)據(jù)包(表示解碼后已發(fā)送完畢) |

reset_info_vld | 1 | I | 復(fù)位信息有效 |

reset_ack | 1 | O | 復(fù)位請(qǐng)求響應(yīng) |

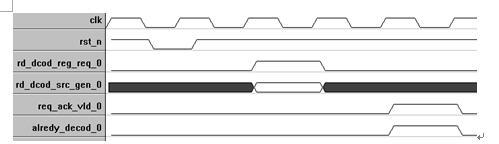

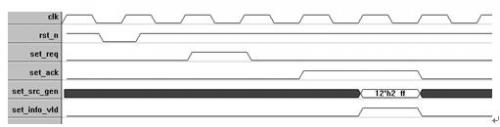

① 讀解碼標(biāo)志

當(dāng)decoder模塊或decode_control_panel讀取解碼標(biāo)志時(shí),將查詢結(jié)果輸出,alredy_decod_0和alredy_decod_1為“1”時(shí)表示本次查詢的數(shù)據(jù)包已經(jīng)解碼,為“0”時(shí)表示未被解碼,以與decoder接口為例,讀取解碼標(biāo)志的時(shí)序如圖3.4-4:

圖3.4-4:讀解碼標(biāo)志位時(shí)序圖

② 寫解碼標(biāo)志位

當(dāng)decoder把一個(gè)數(shù)據(jù)包解碼成功后,就把相應(yīng)的解碼標(biāo)志位置1,當(dāng)SRAM_control將一個(gè)數(shù)據(jù)包發(fā)送出去后,再將相應(yīng)的解碼標(biāo)志位置0,以置位為例,解碼標(biāo)志位的寫時(shí)序如圖3.4-5:

圖3.4-5:置位解碼標(biāo)志寄存器

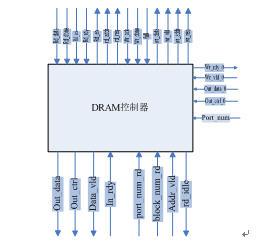

4、DRAM控制器:接收數(shù)據(jù),并順序存儲(chǔ)到DRAM中去。

注意:我們將DRAM分為三塊,分別對(duì)應(yīng)于數(shù)據(jù)接收的三個(gè)信道,即第0個(gè)信道的數(shù)據(jù)存儲(chǔ)到DRAM的第0塊,第1個(gè)信道的數(shù)據(jù)存儲(chǔ)到DRAM的第1塊……信道號(hào)由port_num給出。由于DRAM是按照block讀寫的,因此每個(gè)block大小為2034字節(jié),位寬為144位。

圖3.4-6:DRAM控制器模塊圖

① DRAM控制器與DRAM的接口與讀寫時(shí)序:

Signal Group | Signal Name | Direction | Bits | Description |

Request Negotiation | p_wr_req | from user logic to block-of-data rd/wr module | 1 | 1=request for write transfer (data are from user logic to DRAM), 0=otherwise |

Request Negotiation | p_wr_ptr | from user logic to block-of-data rd/wr module | PKT_MEM_PTR_WIDTH | the start address of DRAM for transfer. Each unit is 16-byte piece |

Request Negotiation | p_wr_ack | from block-of-data rd/wr module to user logic | 1 | 1=the arbiter acknowledges that the write requester can proceed, 0=otherwise |

Data Transfer | p_wr_data_vld | from user logic to block-of-data rd/wr module | 1 | 1=the write data is valid, 0=otherwise |

Data Transfer | p_wr_data | from user logic to block-of-data rd/wr module | PKT_DATA_WIDTH | the data transferred from user logic to DRAM |

Data Transfer | p_wr_full | from block-of-data rd/wr module to user logic | 1 | 1=notify the user logic to pause transfer the next clock cycle until this signal is deasserted, 0=otherwise |

Data Transfer | p_wr_done | from block-of-data rd/wr module to user logic | 1 | 1=this is the last write and no more write will be accepted for this block-of-data, 0=otherwise |

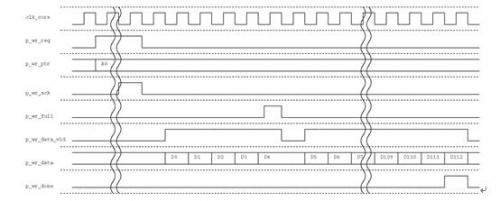

寫DRAM時(shí)序如圖3.4-7:

圖3.4-7 寫DRAM時(shí)序圖

讀端口:

Signal Group | Signal Name | Direction | Bits | Description |

Request Negotiation | p_rd_req | from user logic to block-of-data rd/wr module | 1 | 1=request for read transfer (data are from DRAM to user logic), 0=otherwise |

Request Negotiation | p_rd_ptr | from user logic to block-of-data rd/wr module | PKT_MEM_PTR_WIDTH | the start address of DRAM for transfer. Each unit is 16-byte piece |

Request Negotiation | p_rd_ack | from block-of-data rd/wr module to user logic | 1 | 1=the arbiter acknowledges that the read requester can proceed, 0=otherwise |

Data Transfer | p_rd_rdy | from block-of-data rd/wr module to user logic | 1 | 1=block-of-data rd/wr module has data for user logic to read, 0=otherwise |

Data Transfer | p_rd_en | from user logic to block-of-data rd/wr module | 1 | 1=user logic reads out one word of data from the block-of-data rd/wr module, 0=otherwise |

Data Transfer | p_rd_data | from block-of-data rd/wr module to user logic | PKT_DATA_WIDTH | data transferred from block-of-data rd/wr module to user logic |

Data Transfer | p_rd_done | from block-of-data rd/wr module to user logic | 1 | 1=this is the last read data and no more data will be read for this block-of-data, 0=otherwise |

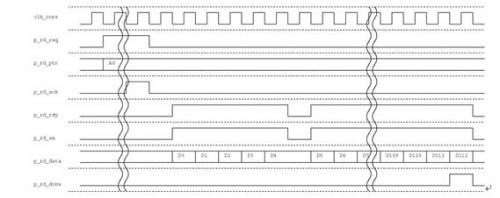

讀DRAM時(shí)序如圖3.4-8:

圖3.4-8 寫DRAM時(shí)序圖

② 其他模塊對(duì)DRAM控制器的讀/寫過(guò)程:

當(dāng)DRAM讀寫控制器將一個(gè)數(shù)據(jù)包讀/寫完之后, 就將rd_idle/wr_rdy_arb置為1,當(dāng)外部模塊需要對(duì)DRAM進(jìn)行讀寫時(shí),首先要判斷這兩個(gè)信號(hào)是否有效,在有效的情況下進(jìn)行對(duì)數(shù)據(jù)的操作。.端口列表如下:

信號(hào)名稱 | 位寬bits | I/O | 描述 |

wr_vld_arb | 1 | I | Input_arbiter輸入有效 |

out_data_0 | 64 | I | 輸入的數(shù)據(jù)包的data_bus |

out_ctrl_0 | 8 | I | 輸入數(shù)據(jù)包的ctrl_bus |

port_num_dram | 2 | I | 輸入信號(hào)的端口號(hào),指明數(shù)據(jù)存放在DRAM的區(qū)域 |

wr_rdy_arb | 1 | O | 寫空閑信號(hào) |

port_num_rd | 2 | I | 讀取數(shù)據(jù)包的區(qū)域 |

addr_vld | 1 | I | 讀地址有效 |

block_num_rd | 8 | I | 數(shù)據(jù)包存放的block的起始地址 |

rd_idle | 1 | O | 讀空閑信號(hào) |

in_rdy | 1 | I | 數(shù)據(jù)輸出輸出允許信號(hào) |

out_data | 64 | O | 讀出的數(shù)據(jù)包的data_bus |

out_ctrl | 8 | O | 輸出數(shù)據(jù)包的ctrl_bus |

data_vld | 1 | O | 輸出數(shù)據(jù)有效 |

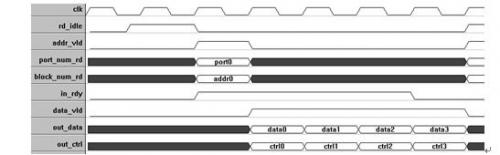

(1)當(dāng)decode_control_panel對(duì)DRAM控制器進(jìn)行讀操作時(shí),將信道號(hào)和block地址發(fā)送至DRAM控制器,接著DRAM控制器從DRAM中讀取數(shù)據(jù),當(dāng)decoder空閑時(shí)將數(shù)據(jù)發(fā)送出去,時(shí)序圖如3.4-9所示:

圖3.4-9 對(duì)DRAM控制器的讀操作

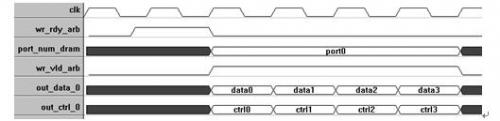

(2)當(dāng)DRAM控制器進(jìn)行寫操作時(shí),將按照input_arbiter發(fā)送過(guò)來(lái)的端口號(hào),按照地址大小順序?qū)慏RAM,時(shí)序圖如3.4-10:

圖3.4-10 對(duì)DRAM控制器的寫操作

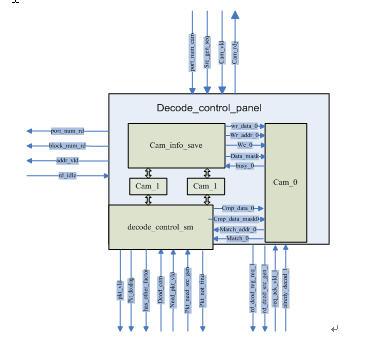

5、decode_control_panel

① 本模塊的內(nèi)部結(jié)構(gòu)圖如3.4-11所示,它由以下五個(gè)模塊組成:cam_info_save, decode_control_sm和3個(gè)CAM組成。

圖3.4-11:decode_control_panel內(nèi)部結(jié)構(gòu)圖

本模塊的輸入輸出端口定義表如下:

端口名稱 | 位寬 bits | I/O | 描述 |

port_num_cam | 2 | In | 數(shù)據(jù)寫入的CAM號(hào),即信道號(hào) |

Src_gen_seq | 24 | In | 輸入數(shù)據(jù)包的信源號(hào)、代編號(hào) |

Cam_vld | 1 | In | 寫有效 |

Cam_rdy | 1 | Out | 寫Cam準(zhǔn)備好 |

rd_idle | 1 | In | DRAM準(zhǔn)備好 |

block_num_rd | 8 | Out | 讀DRAM的地址 |

addr_vld | 1 | Out | 讀地址有效 |

port_num_rd | 2 | out | 要讀取的DRAM的編號(hào) |

Pkt_vld | 1 | Out | 要解碼的數(shù)據(jù)包輸出有效標(biāo)志 |

Pkt_decoding | 12 | out | 正在解碼的數(shù)據(jù)包的信源號(hào)、代編號(hào) |

Decod_com | 1 | In | 數(shù)據(jù)包解碼完成標(biāo)志 |

has_other_factor | 1 | Out | 有另外一個(gè)解碼因子 |

Pkt_not_find | 1 | Out | 所需要解碼數(shù)據(jù)包未找到 |

pkt_need_src_gen | 12 | In | 解碼需要的數(shù)據(jù)包 |

need_pkt_vld | 1 | In | 所需數(shù)據(jù)包有效 |

rd_dcod_reg_req_1 | 1 | Out | 讀解碼標(biāo)志寄存器請(qǐng)求 |

req_ack_vld_1 | 1 | In | 標(biāo)志位有效 |

Alredy_Decod_1 | 1 | In | 解碼標(biāo)志位 |

rd_dcod_src_gen_1 | 12 | out | 查詢數(shù)據(jù)包是否已經(jīng)解碼 |

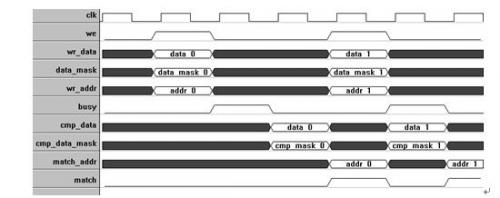

② cam_info_save:

該模塊的主要功能是將輸入的數(shù)據(jù)包的信源號(hào)和代的編號(hào)按地址大小順序存入到三個(gè)cam中,每個(gè)cam分別對(duì)應(yīng)于三個(gè)數(shù)據(jù)輸入通道。每個(gè)CAM的大小是24bits×256,我們要求CAM的讀寫操作可以同時(shí)進(jìn)行,寫數(shù)據(jù)從DIN進(jìn)入,而讀(查詢)的數(shù)據(jù)從CMP_DIN進(jìn)入,寫操作時(shí)BUSY信號(hào)有效,表示不可以響應(yīng)其他寫請(qǐng)求,圖3.4-12是一個(gè)CAM的讀寫操作時(shí)序:

圖3.4-12:CAM讀寫過(guò)程

評(píng)論