復雜處理器的上電時序設計

為確保芯片能可靠的工作,應用處理器的上下電通常都要遵循一定時序, 本文以i.MX6UL應用處理器為例,設計中就必須要滿足芯片手冊的上電時序、掉電時序,否則在產品使用時可能會出現以下情況,第一,上電階段的電流過大;第二,器件啟動異常;第三,最壞的情況會對處理器造成不可逆的損壞。可見,上下電時序對于確保系統的可靠運行起著重要的作用。

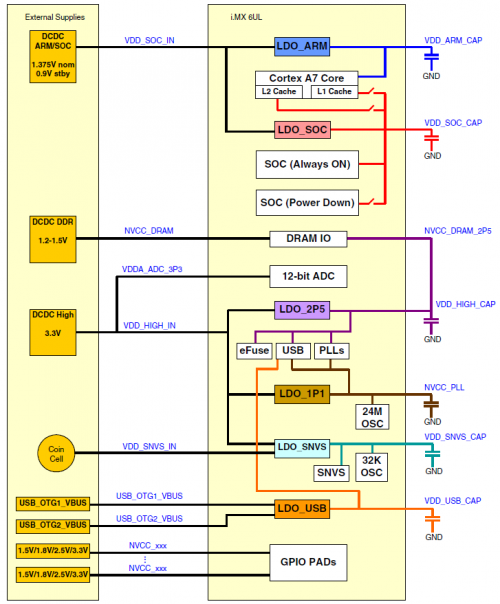

本文引用地址:http://www.104case.com/article/201805/380143.htm為確保芯片能可靠的工作,應用處理器的上下電通常都要遵循一定時序,以i.MX6UL應用處理器為例,設計中就必須要滿足芯片手冊的上電時序、掉電時序,否則在產品使用時可能會出現以下情況,第一,上電階段的電流過大;第二,器件啟動異常;第三,最壞的情況會對處理器造成不可逆的損壞。可見,上下電時序對于確保系統的可靠運行起著重要的作用。以下對i.MX6UL的電源框圖進行說明,然后對其上電時序、掉電時序電路設計進行介紹。

一、i.MX6UL上下電時序要求

上電時序:

1.VDD_SNVS_IN 必須單獨或與VDD_HIGH_IN 一起(短接)上電,在這之后其他電源才能上電。

2.如果使用紐扣電池為VDD_SNVS_IN 供電,請確保在開啟任何其他電源之前將其連接。

3.應在VDD_SOC_IN 之前開啟VDD_HIGH_IN。

掉電時序:

1.VDD_SNVS_IN 必須單獨或與VDD_HIGH_IN 一起(短接)下電,在這之前其他電源必須全部完成下電。

2.如果使用紐扣電池為VDD_SNVS_IN 供電,請確保在關閉任何其他電源之后將其移除。

二 、i.MX6UL電源管理單元-PMU

三、要點分析

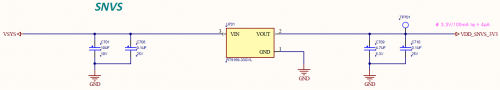

1.從i.MX6UL電源管理單元圖可知,最先供電的VDD_SNVS_IN管腳是作為內部LDO_SNVS的輸入,其輸出電壓VDD_SNVS_CAP是向SNVS模塊及實時時鐘模塊OSC32K供電。 如需在掉電情況下保持RTC,則VDD_SNVS_IN需單獨進行供電,否則可以與VDD_HIGH_IN接一起。VDD_SNVS_IN設計中可預留紐扣電池方案,以滿足掉電保持實時時鐘的應用需求,但如果使用紐扣電池為VDD_SNVS_IN 供電,請確保在開啟任何其他電源之前將其連接。

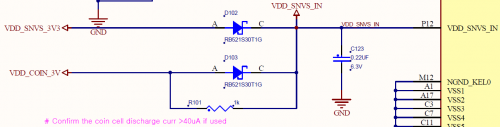

2.由前面上電時序可知,VDD_HIGH_IN可與VDD_SNVS_IN電源一起最先上電。在系統需要掉電保持實時時鐘的情況下,由于VDD_HIGH_IN功耗較高,因此在保持實時時鐘的情況下,需要將該兩路電源需要分開處理。可利用SNVS電源域下的控制信號PMIC_ON_REQ使能后上電的電源模塊,以達到上電的時序要求,如下圖所示。

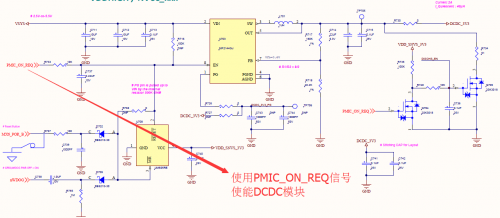

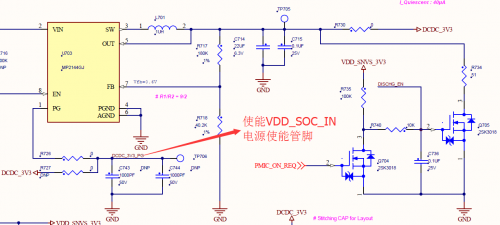

3.由上電時序可知,VDD_SOC_IN上電時序要遲于VDD_HIGH_IN,因此在電路設計中,可使用VDD_HIGH_IN電源芯片的控制信號使能VDD_SOC_IN的電源,如下圖所示為使用VDD_HIGH_IN供電芯片的PG信號使能VDD_SOC_IN供電芯片的使能管腳。

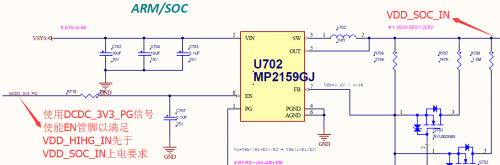

使用DCDC_3V3_PG控制VDD_SOC_IN電源使能管腳以滿足VDD_HIGH_IN上電先于VDD_SOC_IN的要求,如下圖所示。

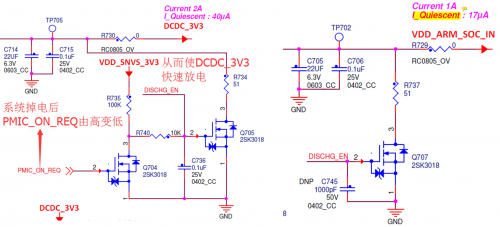

4.根據掉電時序要求,掉電優先順序只要滿足 VDD_SNVS_IN最后掉電即可。設計中加入相應的可控掉電電路,可使后級的濾波電容快速放電從而實現掉電的先后順序,如下圖所示為DCDC_3V3的掉電電路,DCDC_3V3為VDD_HIGH_IN供電。工作原理:系統掉電后,PMIC_ON_REQ由高電平變為低電平,從而使DISCHG_EN信號變為高電平,從而使DCDC_3V3電流通過電阻R734及MOS管Q705導通到GND, VDD_SOC_IN電壓通過DISCHG_EN信號控制MOS管Q707快速掉電,如下圖所示。

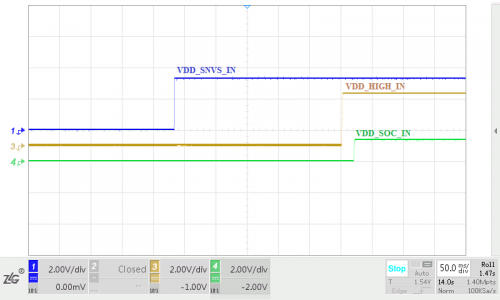

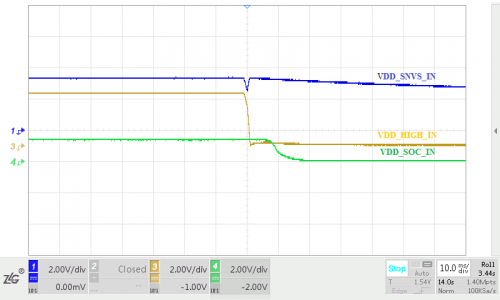

i.MX6UL上電時序波形如下圖所示,其中VDD_SOC_IN為內核電壓-1.35V。

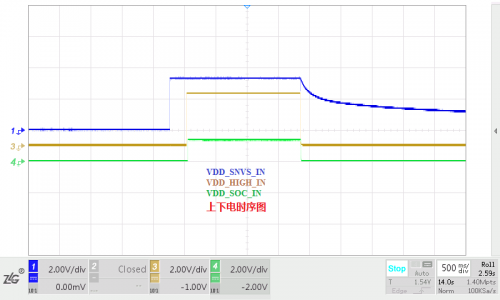

i.MX6UL掉電時序波形如下圖所示。

上下電時序完整波形圖如下圖所示。

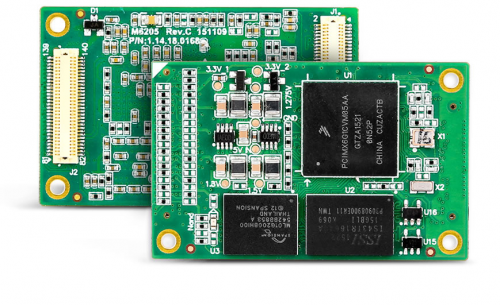

M6G2C采用i.MX6UL處理器,滿足芯片手冊嚴格的上下電時序,是一款工業控制核心板,采用 Freescale Cortex-A7 528MHz主頻的處理器,以先進的電源管理架構帶來更低功耗。標配8路UART、2路USB OTG、2路CAN-Bus、2路以太網等接口;標配128/256MB DDR3和128/256MB NAND Flash、硬件看門狗;通過嚴格EMC和高低溫測試,確保核心板在嚴酷的環境下穩定工作。

評論