VHDL結(jié)構(gòu)體的結(jié)構(gòu)化描述法

結(jié)構(gòu)化描述通常用于層次式設(shè)計(jì)。在8位比較器的實(shí)體設(shè)計(jì)中,實(shí)體說明僅說明了該實(shí)體的I/O關(guān)系,而設(shè)計(jì)中采用的標(biāo)準(zhǔn)元件8輸入與門and 8和二輸入異或非門xnor2是標(biāo)準(zhǔn)元件。它的輸入關(guān)系也就是and8與xnor2的實(shí)體說明,是用USE從句的方式從庫中調(diào)用的。

對于一個(gè)復(fù)雜的電子系統(tǒng),可以分解成許多子系統(tǒng),子系統(tǒng)再分解成模塊。多層次設(shè)計(jì)可以使設(shè)計(jì)多人協(xié)作,并行同時(shí)進(jìn)行。多層次設(shè)計(jì)的每個(gè)層次都可以作為一個(gè)元件,再構(gòu)成一個(gè)模塊或構(gòu)成一個(gè)系統(tǒng),每個(gè)元件可以分別仿真,然后再整體調(diào)試。

結(jié)構(gòu)化描述不僅是一個(gè)設(shè)計(jì)方法,而且是一種設(shè)計(jì)思想,是大型電子系統(tǒng)設(shè)計(jì)高層主管人員必須掌握的。

除了一個(gè)常規(guī)的門電路,其標(biāo)準(zhǔn)化后作為一個(gè)元件放在庫中調(diào)用,用戶自己定義的特殊功能的元件也可以放在庫中,以方便調(diào)用。這個(gè)過程稱為標(biāo)準(zhǔn)化,有的資料中稱為例化。尤其需要聲明的是,元件標(biāo)準(zhǔn)化不僅僅是常規(guī)門電路,這和標(biāo)準(zhǔn)化元件的含義不一樣。即任何一個(gè)用戶設(shè)計(jì)的實(shí)體,無論功能多么復(fù)雜,復(fù)雜到一個(gè)數(shù)字系統(tǒng),如一個(gè)CPU,還是多么簡單,簡單到一個(gè)門電路,如一個(gè)倒相器,都可以標(biāo)準(zhǔn)化成一個(gè)元件。現(xiàn)在在EDA工程中,工程師們把復(fù)雜的模塊程序稱為軟核(softcore或IP core),調(diào)試仿真通過的集成電路版圖稱為硬核,而把簡單的通用模塊稱為元件。

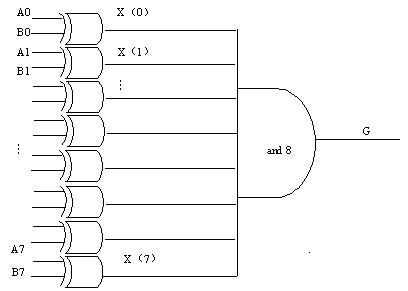

圖1是一個(gè)8位比較器的邏輯電路圖,其對應(yīng)的結(jié)構(gòu)化描述(structural description)程序如例1-9所示。

圖1 8位比較器的邏輯電路圖

【例1-9】 8位比較器的結(jié)構(gòu)化描述法

LIBRARY IEEE;

USE IEEE std_logic_1164.ALL;

ENTITY comparator IS

PORT (a,b: in std_logic_vector(7 downto 0);

g:out std_logic);

END comparator;

USE work.gatespkg.ALL

ARCHITECTURE structural OF comparator IS

signal x: std_logic(0 TO 7);

BEGIN

u0:xnor2 PORT MAP (a(0),b(0),x(0));

u1:xnor2 PORT MAP (a(1),b(1),x(1));

u2:xnor2 PORT MAP (a(2),b(2),x(2));

u3:xnor2 PORT MAP (a(3),b(3),x(3));

u4:xnor2 PORT MAP (a(4),b(4),x(4));

u5:xnor2 PORT MAP (a(5),b(5),x(5));

u6:xnor2 PORT MAP (a(6),b(6),x(6));

u7:xnor2 PORT MAP (a(7),b(7),x(7));

u8:xnor2 PORT MAP (x(0),x(1),x(2),x(3),x(4),x(5),x(6),x(7),

x(8),g);

END structural;

評論