VHDL設計電路優化問題

近年來,隨著集成電路技術和EDA技術的不斷發展,集設計、模擬、綜合和測試功能為一體的VHDL語言,已作為IEEE標準化的硬件描述語言。由于其在語法和風格上類似于現代高級匯編語言,具有良好的可讀性,描述能力強,設計方法靈活,易于修改,又具有可移植性,可重復利用他人的IP模塊 (具有知識產權的功能模塊)等諸多優勢而成為EDA設計方法的首選。VHDL設計是行為級設計,所帶來的問題是設計者的設計思考與電路結構相脫節。設計者主要是根據VHDL的語法規則,對系統目標的邏輯行為進行描述,然后通過綜合工具進行電路結構的綜合、編譯和優化,并通過仿真工具進行邏輯功能仿真和系統時延的仿真。實際設計過程中,由于每個工程師對語言規則和電路行為的理解程度不同,每個人的編程風格各異,往往同樣的系統功能,描述的方式不一,綜合出來的電路結構更是大相徑庭。即使最終綜合出的電路都能實現相同的邏輯功能,但其電路的復雜程度和時延特性差別很大,甚至某些臃腫的電路還會產生難以預料的問題。因此,對VHDL設計中簡化電路結構,優化電路設計的問題進行深入探討,很有必要。

本文引用地址:http://www.104case.com/article/201706/349170.htmVHDL電路設計的優化與VHDL描述語句、EDA工具以及可編程器件(PLD)的選用都有著直接的關系。設計人員首先應注意到以下基本問題:

① PLD器件的邏輯資源是有限的。

② 可編程器件具有特定的結構,應注意器件結構與實際系統的匹配,使系統性能達到最佳。

③ 不是所有的設計都能實現到任意選擇的結構中去。

④ 電路優化的目標相當于求最優解的問題。

1 VHDL設計中提高硬件綜合效率的主要策略

VHDL作為一種硬件描述和仿真語言,最終要實現的是實際硬件電路。但是其設計初衷并非綜合,某些語句并不被綜合器支持,所以在選擇語句時應考慮到綜合與仿真的效率。只有使用綜合工具支持的語句,設計出的程序才有意義。在編程時要注意以下幾點:

① 盡量不使用WAIT FOR XX ns語句和AFTER XX ns語句。XX ns表明在執行下一操作之前需要等待的時間,但綜合器不予支持,一般忽略該時間,而不會綜合成某種元件,故對于包含此類語句的程序,仿真結果與綜合結果往往不一致。

② 聲明信號和變量時盡量不賦初值,定義某確定數值時,使用常量而不用變量賦初值的形式。因為大多數綜合工具將忽略賦值等初始化語句,諸如:VARIABAL S∶INTEGER∶=0。

③ 函數或過程調用時盡量使用名稱關聯。因為名稱關聯可以比位置關聯更好地防止產生不正確的端口連接和元件聲明,也不要在同一個語句中同時使用兩種關聯。諸如:

clk_1:bufes port map(I=>clock_in,clock_out);(不正確的用法)

clk_1:bufes port map(I=>clock_in,O=>clock_out);(正確的用法)

④ 正確使用when_else語句、if_else語句和case語句。VHDL設計電路的復雜程度除取決于設計功能的難度外,還受設計工程師對電路描述方法的影響。最常見的使電路復雜化的原因之一是,設計中存在許多本不必要的類似LATCH的結構,并且這些結構通常都由大量的觸發器組成,不僅使電路更復雜,工作速度降低,而且由于時序配合的原因還會導致不可預料的結果。例如,描述譯碼電路時,由于每個工程師的寫作習慣不同,有的喜歡用IF.。.ELSE 語句,有的喜歡用WHEN.。.ELSE方式,而用IF.。.ELSE時,稍不注意,在描述不需要寄存器的電路時沒加ELSE,則會引起電路不必要的開銷。

例程1: if ina=″00000″ then

Outy<=″0000111″;

elsif ina=″00001″ then

Outy<=″0001000″;

elsif ina=″00010″ then

Outy<=″0001001″;

……

else

Outy<=″0000000″;

end if;

例程2: Outy<=″0000111″ when ina=″00000″ else

″0001000″ when ina=″00001″ else

″0001001″ when ina=″00010″ else

……

″0000000″;

例程2由于使用WHEN.。.ELSE完整條件語句,不會生成鎖存器結構,所以不會有問題。而例程1若不加else Outy<=″0000000″語句,則屬于不完整條件表達方式,會生成一個含有7位寄存器的結構。雖然上述例程都能實現相同的譯碼功能,但是電路復雜度會大不相同。

⑤ 注意算術功能的設計優化。例如下面兩條語句:

Out=A+B+C+D;

Out=(A+B)+(C+D);

第一條語句綜合后將會連續疊放3個加法器(((A+B)+C)+D);第二條語句(A+B)和(C+D)使用兩個并行的加法器,同時進行加法運算,再將運算結果通過第三個加法器進行組合。雖然使用資源數量相同,但第二條語句速度更快。以4位和16位加法器為例,選用Altera公司 EPF10K30AQC240_3芯片,通過synopsys FPGA Express綜合工具實現的結果進行測試,比較結果如表1所列。

2 優化系統速度的VHDL設計策略

選用基于VHDL設計的CPLD/FPGA器件往往首先是為了滿足高速運行的需要,如通信系統。系統運行速度與電路節點之間的延時直接相關,因此,減少冗余邏輯,縮短節點延時是提高系統速度的關鍵。速度優化與電路結構設計(如器件結構特性、系統電路構成和PCB制板情況)和軟件使用(如綜合器性能和 VHDL描述方式)都有關系。

2.1 電路結構方面速度優化的主要方法

① 流水線設計是最常用的速度優化技術。采用流水線設計雖然不能縮短總工作周期,但通過把一個工作周期內的邏輯操作分成幾步較小操作,并連續同步實現的策略,可大大提高系統總體運行速度。

② 合理使用嵌入式陣列塊EAB資源和LPM宏單元庫。在DSP、圖像處理等領域,乘法器是應用最廣泛、最基本的模塊,其速度往往制約著整個系統性能。而EAB是PLD器件中非常有效的高速資源,利用EAB單元和參數化模塊LPM,可以設計出乘法器等高速電路。

③ 關鍵路徑優化。所謂關鍵路徑是指從輸入到輸出延時最長的邏輯通道。關鍵路徑優化是保證系統速度優化的有效方法。

2.2 軟件使用方面速度優化的方法

一般EDA軟件尤其是綜合器,均會提供一些針對具體器件和設計的優化選項。設計者在使用軟件時應注意根據優化目標的要求,適當修改軟件設置。在MAX+plusII中,就可以使用Assign/Device命令選擇不同速度等級的芯片。

3 面積優化的VHDL設計策略

面積優化是提高芯片資源利用率的另一種方法,通過面積優化可以使用規模更小的芯片,從而降低成本和功耗,為以后技術升級預留更多資源。面積優化最常用的方法是資源共享和邏輯優化。

3.1 資源共享方法

資源共享的主要思想是通過數據緩沖或多路選擇的方法來共享數據通道中占用資源較多的模塊(如乘法器、多位加法器等算術模塊)。

例程3: process(A0,A1,B,sel)

begin

if(sel=‘0’)then result=A0*B;

else result=A1*B;

end if;

end processs;

例程4: process(A0,A1,B,sel)

begin

if(sel=‘0’)then temp=A0;

else temp=A1;

end if;

result=temp*B;

end processs;

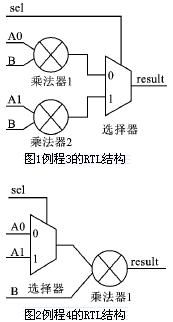

例程3的設計可用圖1描述,例程4的設計可用圖2描述。可見例程4節省了一個代價高昂的乘法器,整個設計占用面積比例程3幾乎減少了一半。

3.2 邏輯優化方法

通過邏輯優化以減少資源利用也是常用的面積優化方法(如常數乘法器的應用,并行邏輯串行化處理等),但其代價往往是速度的犧牲。在延時要求不高的情況下,采用這種方法可以達到減少電路復雜度、實現面積優化的目的。

4 結論

通過以上初步的探討可知,用VHDL進行集成電路的設計,不僅需要熟悉VHDL語言的使用方法和對設計要求的深刻理解,而且應在設計全程中遵循最優化設計的基本原則,在電路結構設計和軟件使用中尋找滿足設計要求的最佳方案。

評論