英特爾:下一代DNN到來時(shí) 未來FPGA能將敗GPU

在最近的FPGA國(guó)際研討會(huì)(ISFPGA)上,英特爾加速器架構(gòu)實(shí)驗(yàn)室(AAL)的Eriko Nurvitadhi博士,發(fā)表題為《Can FPGAs beat GPUs in Accelerating Next-Generation Deep Neural Networks》的報(bào)告,分享了英特爾的最新研究。

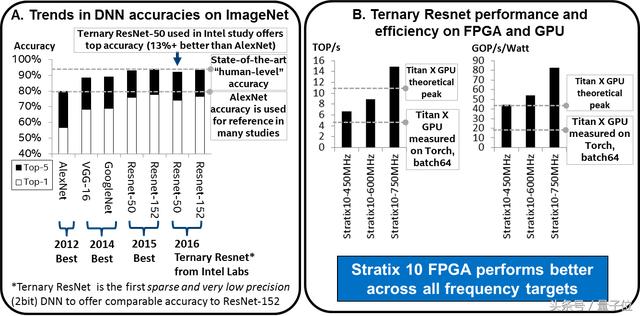

本文引用地址:http://www.104case.com/article/201703/345681.htm這一研究,主要評(píng)估在DNN(深度神經(jīng)網(wǎng)絡(luò))算法領(lǐng)域,兩代英特爾FPGA(Intel Arria10和Intel Stratix 10),與NVIDIA TITAN X Pascal GPU相比性能如何。

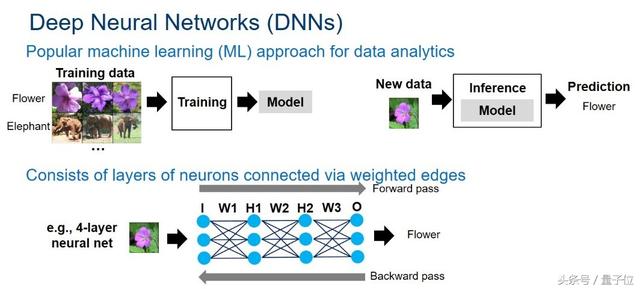

△ 深度神經(jīng)網(wǎng)絡(luò)概述

英特爾表示在應(yīng)用領(lǐng)域,F(xiàn)PGA在DNN研究中表現(xiàn)非常出色,可用于需要分析大量數(shù)據(jù)的AI、大數(shù)據(jù)或機(jī)器學(xué)習(xí)等領(lǐng)域。使用經(jīng)修剪或緊湊的數(shù)據(jù)類型與全32位浮點(diǎn)數(shù)據(jù)(FP32)時(shí),測(cè)試的Intel Stratix 10 FPGA的性能優(yōu)于GPU。

除了性能外,F(xiàn)PGA還具有強(qiáng)大的功能,因?yàn)樗鼈兙哂羞m應(yīng)性,通過重用現(xiàn)有的芯片可以輕松實(shí)現(xiàn)更改,從而讓團(tuán)隊(duì)在六個(gè)月內(nèi)從一個(gè)想法進(jìn)入原型。

而構(gòu)建一個(gè)ASIC需要18個(gè)月。

FPGA重要性正在提升

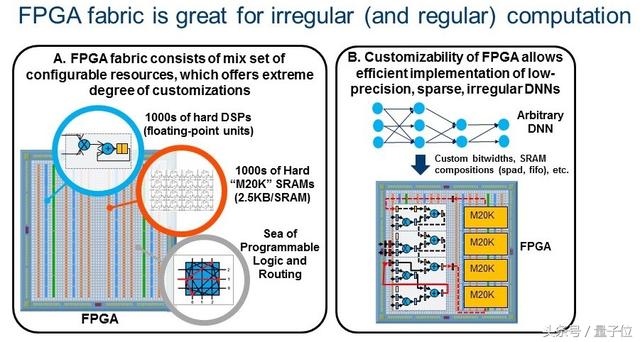

△ FPGA非常適用于DNN

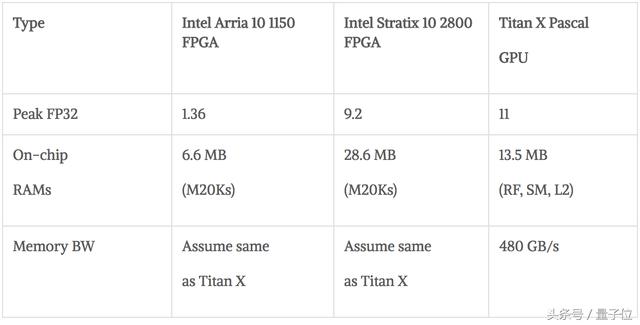

硬件:與高端GPU相比,F(xiàn)PGA具有卓越的能源效率(性能/瓦特),但還有不被熟知的高峰值浮點(diǎn)性能。FPGA技術(shù)正在迅速發(fā)展。即將推出的英特爾Stratix 10 FPGA提供超過5,000個(gè)硬件浮點(diǎn)單元(DSP),超過28MB的片上RAM(M20K),與高帶寬內(nèi)存等特性。

基于14nm工藝的英特爾Stratix 10在FP32吞吐量方面達(dá)到峰值9.2TFLOP/s。相比之下,最新的Titan X Pascal GPU的FP32吞吐量為11TFLOP/s。

新興的DNN算法:更深的網(wǎng)絡(luò)提高了精度,但是大大增加了參數(shù)和模型大小。這增加了對(duì)計(jì)算、帶寬和存儲(chǔ)的需求。因此,新興趨勢(shì)是采用緊湊型低精度數(shù)據(jù)類型,遠(yuǎn)低于32位。16位和8位數(shù)據(jù)類型正在成為新常態(tài),也得到DNN軟件框架(例如TensorFlow)的支持。

新興的低精度和稀疏DNN算法比傳統(tǒng)的密集FP32 DNN提供了數(shù)量級(jí)的算法效率改進(jìn),但是它們引入了難以處理的不規(guī)則并行度和定制數(shù)據(jù)類型。這時(shí)FPGA的優(yōu)勢(shì)就體現(xiàn)出來了。這種趨勢(shì)使未來FPGA成為運(yùn)行DNN,AI和ML應(yīng)用的可行平臺(tái)。

研究所用的硬件和方法

GPU:使用已知的庫(kù)(cuBLAS)或框架(Torch with cuDNN)

FPGA:使用Quartus Early Beta版本和PowerPlay

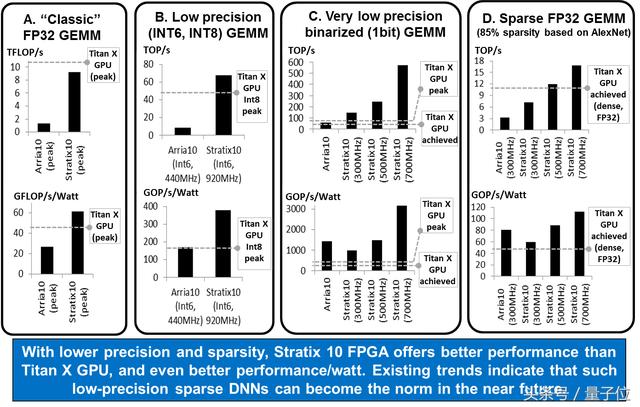

研究一:矩陣乘法(GEMM)測(cè)試

矩陣乘法(GEMM)測(cè)試的結(jié)果。GEMM是DNN中的關(guān)鍵操作,上述四個(gè)不同類型的測(cè)試表明,除了在FP32 Dense GEMM測(cè)試中,Stratix 10與TITAN X仍有差距。另外三項(xiàng)測(cè)試中新一代英特爾FPGA的表現(xiàn)都優(yōu)于GPU。

研究二:使用三元ResNet DNNs測(cè)試

三進(jìn)制DNN最近提出約束神經(jīng)網(wǎng)絡(luò)權(quán)重為+1,0或-1。這允許稀疏的2位權(quán)重,并用符號(hào)位操作代替乘法。與許多其他低精度和稀疏的DNN不同,三元DNN可以提供與現(xiàn)有技術(shù)DNN(即ResNet)相當(dāng)?shù)木取?/p>

上圖右半部分,顯示了英特爾Stratix 10 FPGA和TITAN X GPU的ResNet-50的性能和性能/功耗比。即使對(duì)于保守的性能估計(jì),英特爾Stratix 10 FPGA已經(jīng)比實(shí)現(xiàn)了TITAN X GPU性能提高了約60%。在性能/功耗比方面,英特爾Stratix 10比TITAN X要好2.3倍到4.3倍。

結(jié)論

再說一次,這個(gè)研究報(bào)告出自英特爾,這個(gè)研究團(tuán)隊(duì)還指出,除了DNN之外,F(xiàn)PGA在其他不規(guī)則應(yīng)用程序以及延遲敏感程序(如ADAS)等領(lǐng)域也有機(jī)會(huì)。

評(píng)論