Intel高級院士曝光自家10nm工藝:集成度比優(yōu)于對手

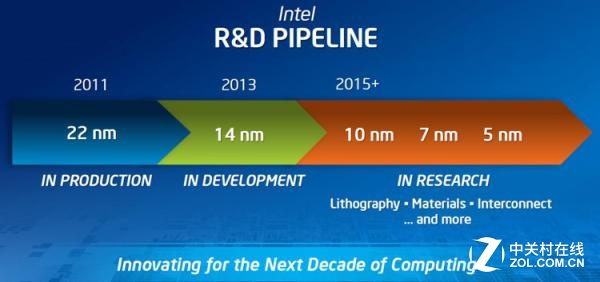

臺積電和三星紛紛量產10nm,而曾經作為半導體工藝技術龍頭的Intel卻動作遲緩,待在14nm上不肯動彈了,10nm目前看最快最快也得2018年下半年。

本文引用地址:http://www.104case.com/article/201701/342480.htm那么,真的是Intel在技術上黔驢技窮了?

顯然不是。Intel在最新一期的半導體行業(yè)權威刊物《IEEE Spectrum》上撰文,暢談了自己的10nm工藝,尤其是在技術、成本方面的巨大優(yōu)勢。

Intel高級院士Mark Bohr表示,Intel 10nm工藝的晶體管密度不但會超過現(xiàn)在的Intel 14nm,還會優(yōu)于其他公司的10nm,也就是集成度比他們更高,柵極間距將從14nm工藝的70nm縮小到54nm,邏輯單元則縮小46%,這比以往任何一代工藝進化都更激進。

他說:“本代工藝和相關產品要傳達的一個重要信息,就是希望能夠打消行業(yè)對于摩爾定律將死的憂慮。”

Intel在技術上的實力其實根本不用懷疑,那么是不是成本限制了10nm?Mark Bohr也談到了這一點,明確表示Intel 10nm晶圓的整體成本確實會高于14nm,但是平均到每個晶體管上會更低。

和每一代新工藝一樣,10nm也能提高晶體管的運行速度,或者降低能耗,但更重要的顯然是后者。

Mark Bohr表示:“這些新工藝的首要目標確實是降低能耗,或者說提高能效,只有這樣才能在服務器芯片內加入更多核心,或者在GPU內加入更多執(zhí)行單元,然后才是降低晶體管成本。”

目前,臺積電、GlobalFoundries(AMD)、三星等都在積極籌劃7nm,Intel的似乎還很遙遠。

Mark Bohr對此表示,如果從10nm過渡到7nm會花更長時間,那么最重要的就是想方設法增強已有技術,每年帶來新產品。

這似乎意味著,在未來至少五年左右的時間里,Intel仍會堅持當前的產品研發(fā)和發(fā)布策略,不會變的太激進。

評論