基于Altera cyclone V SOC的JPEG編碼分析

H.264等視頻壓縮算法在視頻會議中是核心的視頻處理算法,它要求在規(guī)定的短時間內(nèi),編解碼大量的視頻數(shù)據(jù),目前主要都是在DSP上運行。未來在添加4k*2k、H.265編解碼等功能,并要求控制一定成本的情況下,面臨DSP性能瓶頸的問題,所以希望部分算法可以下放到FPGA來實現(xiàn),借助FPGA并行處理的優(yōu)勢,來加速整個系統(tǒng)。

本文引用地址:http://www.104case.com/article/201610/308566.htm基于altera cyclone V soc平臺的試驗可行性分析

1.JPEG圖像壓縮算法與H.264等視頻壓縮算法,有一定的相似性,并要簡單很多,有一定的借鑒意義,故本次短期試驗使用JPEG算法來驗證該SOC平臺;

2.JPEG壓縮算法如果完全在FPGA上用VerilogHDL語言實現(xiàn),有一定難度,并且開發(fā)周期很長,而C語言源碼,已經(jīng)比較成熟,移植到ARM比較簡單;

3.經(jīng)考察,altera cyclone V soc平臺,擁有兩顆速度高達(dá)800Mhz的cortex A9內(nèi)核,并有大容量的邏輯單元,和高速收發(fā)模塊。FPGA與ARM之間的AXI標(biāo)準(zhǔn)總線,速度更是高達(dá)100Gbit,對傳輸高清視頻數(shù)據(jù),即使4K*2K也是綽綽有余。

試驗過程

JPEG是Joint Photographic Experts Group的縮寫,即ISO和IEC聯(lián)合圖像專家組,負(fù)責(zé)靜態(tài)圖像壓縮標(biāo)準(zhǔn)的制定,這個專家組開發(fā)的算法就被稱為JPEG算法,并且已經(jīng)成為了大家通用的標(biāo)準(zhǔn),即JPEG標(biāo)準(zhǔn)。JPEG壓縮是有損壓縮,但這個損失的部分是人的視覺不容易察覺到的部分,它充分利用了人眼對計算機(jī)色彩中的高頻信息部分不敏感的特點,來大大節(jié)省了需要處理的數(shù)據(jù)信息。

JPEG編碼中主要涉及到的內(nèi)容主要包括:

1. Color Model Conversion(色彩模型)

2. DCT(Discrete Cosine Transform離散余弦變換

3.重排列DCT結(jié)果

4.量化

5. RLE編碼

6.范式Huffman編碼

7. DC的編碼

本次試驗ARM側(cè)運行LINUX操作系統(tǒng),并將Color Model Conversion部分,下發(fā)給FPGA側(cè)來實現(xiàn),如上圖,黃色區(qū)域標(biāo)記。其中ARM核與FPGA的數(shù)據(jù)交互運用了HPS-to-FPGA x64 Bridge,該總線的讀寫操作都是在MMAP(將底層地址空間映射到用戶層)后,通過使用HWlib庫函數(shù)來實現(xiàn)。在FPGA側(cè),運用Qsys工具,添加Application_logic用戶邏輯模塊,來實現(xiàn)Color Model Conversion功能,如下圖黃色區(qū)域標(biāo)記。

試驗結(jié)果

1.整個編碼過程正常,以下左側(cè)為編碼前的真彩。bmp格式圖片,右側(cè)為編碼后的。jpg格式圖片。

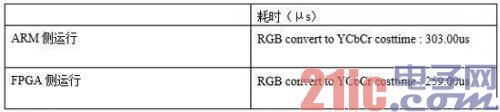

2.通過調(diào)用LINUX操作系統(tǒng)時鐘函數(shù)gettimeofday( Model Conversion部分在ARM側(cè)運行,和在FPGA側(cè)運行消耗的時間:

從表中可以看出,F(xiàn)PGA在大數(shù)據(jù)量的處理時,能發(fā)揮并行的優(yōu)勢,使運算速度得到提升。因試驗開發(fā)程度有限,所以速度提升不是很明顯。相信在將更多數(shù)據(jù)處理任務(wù)交給FPGA完成后,能獲得更高的系統(tǒng)性能。

試驗結(jié)論

1. cycloneV SOC有ARM核的存在,可以運用成熟的C語言代碼,縮短開發(fā)時間;

2. cycloneV SOC有大量邏輯單元,可以協(xié)助處理大量數(shù)據(jù),提高系統(tǒng)性能;

3. cycloneV SOC成本低廉,滿足成本控制要求;

評論