采用 Zynq SoC 測試新型存儲器技術芯片

基于賽靈思 ZC706 評估套件的平臺被證實用作高通的 MRAM 測試,足夠快速靈活。

本文引用地址:http://www.104case.com/article/201601/286357.htm作者:Botao Lee 資深工程師 高通科技 blee@qti.qualcomm.com

Baodong Liu 高級工程師 高通科技 baodongl@qti.qualcomm.com

Wah Hsu 資深工程師 高通科技 wahh@qti.qualcomm.com

Bill Lu 高級工程師 高通科技 xiaolu@qti.qualcomm.com

電子產業正在大力投資開發PRAM、MRAM和RRAM等新型存儲器技術。新型存儲器技術測試芯片的性能快速提高,但這種存儲器要做到能與傳統存儲器全面抗衡乃至取代傳統存儲器還需要更多的努力。

通常說來,有了新型存儲器技術的測試芯片,能夠完成制造相關的基礎測試,例如會檢查固化故障、轉換故障和地址解碼故障等。同時還有一種測試也是必需的,那就是要進行性能相關的測試,了解芯片可靠存取的速度能有多快,以及芯片存取速度如何影響整個計算系統性能。

為了成功進行規劃的性能測試,測試環境必須能夠生成可配置的數字波形來存取芯片。同時還要創建整個計算環境來測量芯片存取速度的影響。創建或購買測試環境、滿足上述需求有多種方法。我們在高通的團隊決定采用賽靈思 Zynq?-7000 All Programmable SoC ZC706 評估套件來打造自己的環境。

存儲器進出

DRAM、SRAM 和閃存等傳統存儲器技術用存儲器單元中的電荷來存儲 0 和 1。DRAM 廣泛被 PC和移動計算設備用來運行程序和存儲臨時數據。SRAM 通常用作微處理器的高速緩存存儲器和寄存器薄,同時也經常用于對功耗問題很敏感的嵌入式系統中。與 DRAM 和 SRAM 不同,閃存存儲器在系統斷電后仍能永久保存數據。閃存存儲器的運行速度比其他存儲器要慢,大量編程循環后可能會磨損。

相對于傳統基于電荷的存儲器技術而言,新型存儲器技術基于存儲元件的其他物理屬性。舉例來說,磁阻 RAM (MRAM) 的存儲器元件由兩個鐵磁板組成,這兩個鐵磁板由一層薄薄的絕緣層隔離。每片鐵磁板都能保有磁化屬性,一個是永久性的,另一個可有外部場改變,從而存儲數據。通過測量元件電阻即能讀取存儲的數據。MRAM 存取速度類似于 SRAM,密度類似于 DRAM。相比于閃存存儲器,MRAM 運行速度更快,而且不會因編程而被磨損。

軟件運行在 Zynq SoC 的 ARM A9 處理器上,而存儲器控制器內核則用可編程邏輯創建。

要求分析

在設計 MRAM 測試芯片評估方案時,我們決定采用 Zynq SoC 方法,這主要出于以下考慮:

? ZC706 開發板的 FPGA 夾層卡 (FMC) 接口通過 FMC 子卡提供進出存儲器測試芯片的高速信號發送功能。

? Zynq SoC 的可編程邏輯 (PL) 部分能構建參數化存儲器控制器內核。這對滿足測試芯片差異化存取速度的要求很重要。

? Zynq SoC 的處理系統 (PS) 包括兩個 ARM? A9 內核,能通過軟件修改測試芯片存取速度。

? PS 也能構建完整的計算系統,這對滿足測試系統在全面計算環境下測量芯片存取速度的影響的要求很重要。

硬件和系統架構

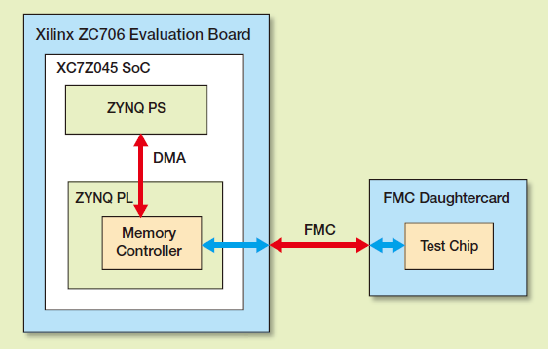

芯片測試環境的硬件架構如圖 1 所示。軟件運行在 Zynq SoC 的 ARM A9 處理器上,而存儲器控制器內核用可編程邏輯創建。我們在 PS 和控制器內核之間建立 DMA 通道,以便在彼此之間能方便地移動大數據塊。存儲器測試芯片位于 FMC 子卡上,其通過 FMC 接口與存儲器控制器內核通信。

系統架構如圖 2 所示。底部三層為硬件層,頂部三層為軟件層。我們選擇 Linux 為操作系統,因為這是一種開源系統,源代碼能根據需要修改。雖然目前開發階段沒有進行修改,但今后這種新型存儲器芯片發揮獨特屬性優勢時或許能用得上。

圖 1 – 測試環境的硬件架構

圖中文字如下:

賽靈思 ZC706 評估板

XC7Z045 SoC

ZYNQ PS

DMA

ZYNQ PL

存儲器控制器

FMC

FMC 子卡

測試芯片

圖 2 – 測試環境的系統架構

我們在應用層編寫的軟件分為兩類。一類用于配置存儲器控制器內核;另一類涉及存儲器芯片和整體系統性能的特性分析。

軟硬件輕松移植

在當地賽靈思現場應用工程師(FAE) 的幫助下,我們一個月就建起了測試環境。我們大部分精力放在設計和實現軟硬件層之間的接口上,這也是我們喜歡 Zynq SoC 的一大原因:它在單個器件中集成了微處理器和可編程邏輯,這就使得軟硬件之間功能遷移變得相當簡單。在我們的設計中,我們幾次微調軟硬件分區,最終才確定我們喜歡的方案。為了在基于 Zynq SoC 的系統上方便地工作,需要比較深入地了解軟硬件。

我們也很喜歡 Vivado? 設計套件工具鏈。Vivado 環境能簡單直觀地展示設計模塊,自動分配寄存器地址并檢查錯誤,然后再導出硬件信息到軟件開發階段。Vivado 設計套件還提供系統內信號級調試功能,這是明確發現 RTL 問題根源的必備功能。

最后我們要提的就是 Linux OS。我們應用層的軟件主要基于 GUI,Linux OS倍受青睞,也讓我們能利用此前 Linux GUI 的開發經驗,從而快速啟動并運行測試程序。

快速和低成本

采用 Zynq-7000 All Programmable SoC ZC706 評估套件,我們的團隊能快速構建完整的計算環境,從而以最低成本測試新型存儲器技術芯片。我們希望有朝一日能用相同的設計方法去構建用于其他目的的類似系統。

評論