時(shí)鐘分配芯片 在高速并行數(shù)據(jù)采集中的應(yīng)用

AD9510是有美國模擬半導(dǎo)體公司推出的一款精確時(shí)鐘分配芯片。它具有2路1.6 GHz的差分時(shí)鐘輸入、8路時(shí)鐘輸出以及片上PLL核。其中,包括4路獨(dú)立的1.2 GHz LVPECL時(shí)鐘輸出。另外4路獨(dú)立的時(shí)鐘輸出可設(shè)置成LVDS或CMOS:設(shè)置成LVDS輸出時(shí),頻率可以達(dá)到800 MHz;設(shè)置成CMOS輸出時(shí),頻率可以達(dá)到250 MHz。同時(shí),該款芯片還能通過SPI串行編程來控制輸出時(shí)鐘間的相位延遲,且抖動(dòng)和相位噪聲極低。

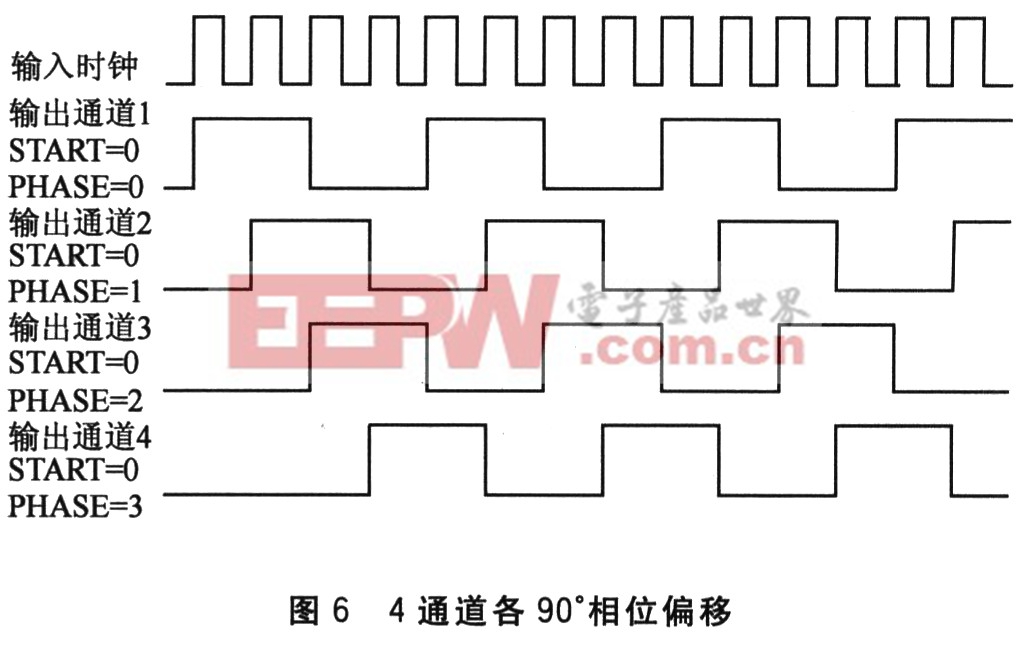

AD9510時(shí)鐘芯片的配置如圖5所示。其中,1、2引腳為PLL時(shí)鐘參考輸入。16腳內(nèi)部接30 kΩ的下拉電阻,可以通過編程實(shí)現(xiàn)復(fù)位、同步和下拉。如果該腳懸空,默認(rèn)作復(fù)位用,所以通常接1 kΩ電阻接地。18~21腳為與MCU的串行通信口。通過串行方式,可以對芯片進(jìn)行設(shè)置。其中,通過49H到57H中奇數(shù)寄存器的配置,可以實(shí)現(xiàn)對每個(gè)通道相位的控制。每個(gè)分頻通道有4位的相位偏移控制和1位起始控制。在同步脈沖來臨后,相位延時(shí)字決定分頻輸出等待多少個(gè)輸入時(shí)鐘周期。相位延時(shí)的起始位決定輸出是從低電平開始,還是從高電平開始。這樣,通過對不同輸出通道參數(shù)的控制,可以很容易實(shí)現(xiàn)通道間相位的90°偏移。4通道各90°相位偏移如圖6所示。

將每個(gè)通道的輸出設(shè)置為4分頻和50%占空比。把通道1設(shè)置為低電平起始,0輸入時(shí)鐘延時(shí);把輸出通道2設(shè)置為低電平起始,1個(gè)輸入時(shí)鐘延時(shí);把輸出通道3設(shè)置為低電平起始,2個(gè)輸入時(shí)鐘延時(shí);把輸出通道4設(shè)置為低電平起始,3個(gè)輸入時(shí)鐘延時(shí)。這樣就實(shí)現(xiàn)了圖6中相位相差90°的4通道輸出。通過時(shí)鐘芯片配置產(chǎn)生相差90°的采樣時(shí)鐘提供給4片采樣芯片AD9481,可以使總的采樣率達(dá)到1 Gsps的水平。

結(jié) 語

本文通過對時(shí)鐘分配芯片AD9510的正確配置,采用ADC芯片AD9481實(shí)現(xiàn)了4個(gè)通道90°相位偏移的高速時(shí)鐘輸出,從而大大提高了系統(tǒng)采集速度。

需要注意的是,多片ADC并行采樣的方式勢必引入通道適配誤差,在后續(xù)的處理上必須引起足夠的重視。

評論