基于ARM和FPGA的微加速度計數據采集系統設計

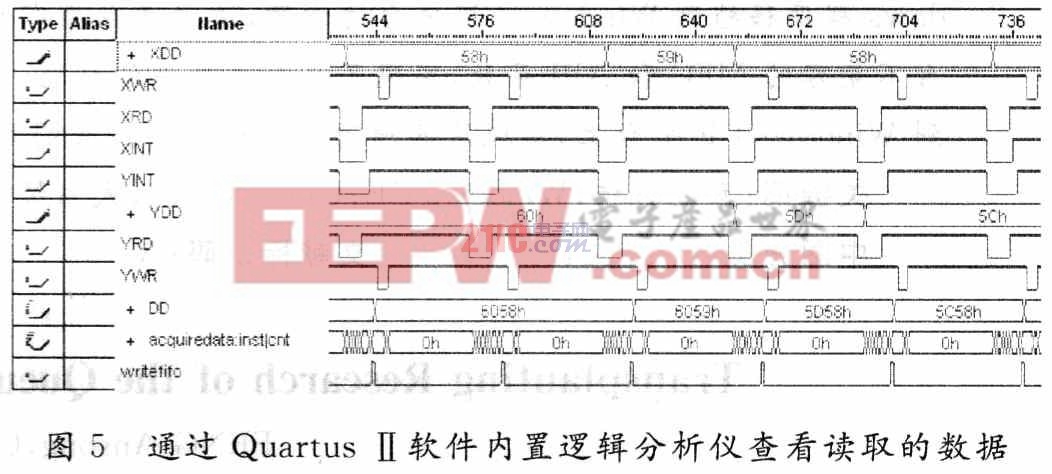

由A/D轉換輸出轉換后的8位數字信號,可以從QuartusⅡ內置的邏輯分析儀中讀取,圖5為通過QuartusⅡ軟件內置邏輯分析儀查看讀取數據值的截圖。從圖5中可以看出在讀寫方式中,在WR/RDY的上升沿開始啟動轉換,到INT的下降沿轉換完成,轉換時間可通過時間標尺計算出來,為24×40=960 ns,之后就可以通過RD的上升沿開始讀取轉換后的數據到數據總線中,如圖5中的XDD以及YDD。因為單片機的處理速度一般都低于A/D轉換芯片的速度,故將XDD與YDD的數據存儲到FPGA中的FIFO中,FIFO便起到數據緩沖的作用,以備接下來單片機對數據進行讀取。本文引用地址:http://www.104case.com/article/195475.htm

3.2 ARM系統接收FPGA數據

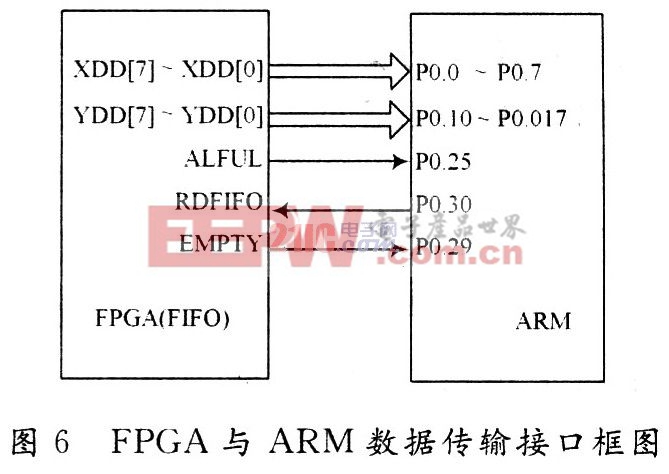

圖6為FPGA與ARM相連接部分的傳輸接口框圖。ARM系統主要控制數據采集的啟動和采集結束后對數據的顯示和存儲,在數據采集的過程中,ARM處理器系統讀取FPGA中的數據,實際上是讀取FIFO中的數據。FIFO的容量可以通過軟件進行設置,它有兩個狀態顯示信號,分別為ALFUL和EMPTY,ALFUL是指FIFO接近滿,當ALFUL從低電平變為高電平后,ARM單片機系統就可以發送RDFIFO信號來讀取FIFO中的數據輸出端口的數據,當FIFO中的EMPTY信號從低電平變為高電平,表明FIFO中已無數據可讀,ARM單片機就開始等待ALFUL的跳變進行下一次的讀取。

3.3 加速度數據顯示和存儲

由ARM系統采集到的數據可通過串口線發送到上位機進行實時顯示,也可以通過模擬IDE通信協議儲存到IDE硬盤中。LPC2210通過串口線與上位機進行通信主要是應用ARM芯片LPC2210中的通用異步接收/發送裝置UART0,而使用LPC2210的通用可編程I/O口,可以模擬產生IDE硬盤的讀寫時序,實現對存儲設備的讀寫操作。這樣可以實現加速度數據的顯示和存儲。

4 結語

這里介紹一種MEMS器件微加速度計的數據采集設計方案,結合當前應用廣泛的處理芯片ARM和FPGA,給出了一種配置靈活、通用性強的數據采集方案。實驗中可準確采集美新加速度計MXR6150G/M的加速度信號,采集到的信號既可以在上位機實時顯示,又可以存儲在IDE接口硬盤中,達到了數據顯示和存儲的目的。

評論