基于ARM和FPGA的微加速度計數據采集系統設計

2.3 Altera-FPGA與ARM處理器

該系統的FPGA采用Altera FPGA公司的CycloneⅡ系列的EP2C35實現,EP2C35提供多達33 216個邏輯單元(LE),35個18×18位乘法器483 840 b的內部RAM塊,專用外部存儲器接口電路,4個鎖相環(PLL)和高速差分I/O等功能。

該系統中采用的ARM處理器是Philips公司的LPC2210,是基于一個支持實時仿真和嵌入式跟蹤的16/32位ARM7TDMI-S CPU的微控制器。 LPC2210的144腳封裝、極低的功耗、兩個32位定時器、八路lO位ADC,PWM輸出以及多達九個外部中斷使其特別適用于工業控制、醫療系統、訪問控制和電子收款機等。通過配置,LPC2210最多可提供76個GPIO。由于內置了寬范圍的串行通信接口,其也非常適合于通信網關、協議轉換器以及其他各種類型的應用。本文引用地址:http://www.104case.com/article/195475.htm

3 采集系統整體實施方案

3.1 FPGA控制A/D芯片進行加速度計數據采集

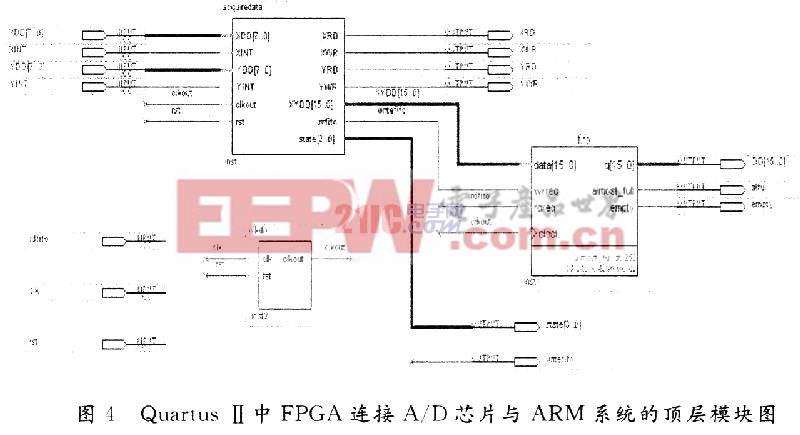

該加速度計是利用兩路模擬電壓輸出來反映加速度值的大小,當加速度值為O時輸出電壓為1.50 V,電壓輸出靈敏度為150 mV/g,A/D轉換器模擬輸入電壓范圍為VCC±0.1 V,低于VREF- +(1/2)LSB或高于VREF+ -(1/2)LSB的模擬輸入電壓分別轉換為00000000或1111111,系統中所加電壓分別為VCC=VREF+=5 V,VREF-=GND=O V。TLC0820可通過MODE的設置工作在只讀和讀寫兩種方式。當MODE為低時,轉換器為只讀方式。在這種方式中,作為輸出,且作為準備輸出端;同時。當為低時,亦為低,表明器件忙,轉換器在的下降沿開始轉換,經過不到2.5μs轉換完成,此時下降.為高阻,數據輸出也由高阻變為有效的數據端,當數據讀出后,變高,返回高,數據輸出端返回到高阻態。當MODE為高時,轉換器為讀/寫方式,作為寫輸出端。當和為低時,轉換器開始測量輸入信號,大約600 ns后返回高,轉換器完成轉換,在讀寫方式中,在上升沿開始轉換。該實驗采用讀寫方式來控制A/D芯片來讀取加速度計的值,所需的控制信號由FPGA輸出,相關的邏輯控制采用Verilog硬件描述語言進行編寫,圖4為QuartusⅡ中FPGA連接A/D芯片與ARM系統的頂層模塊圖。

評論