基于ARM和FPGA的微加速度計數據采集系統設計

摘要:基于常用的MEMS慣性器件微型加速度計,介紹一種采用ARM和FPGA架構來采集加速度數值的設計方案,微加速度計的模擬輸出信號經A/D芯片轉換后由FPGA進行處理和緩存,然后ARM接收FPGA的輸出數據并對數據進行顯示和存儲.對如何用FPGA實現該數據采集系統的傳輸控制和數據緩存,以及FPGA與A/D轉換芯片和ARM的接口設計給出了說明,實現了加速度數值的采集、傳輸、顯示和存儲,該方法配置靈活、通用性強,可以較好地移植到相關器件的數據采集系統中。

關鍵詞:數據采集;微加速度計;FPGA;ARM;TLC0820

0 引言

加速度計是一種應用十分廣泛的慣性傳感器,它可以用來測量運動系統的加速度。目前的加速度計大多采用微機電技術(MEMS)進行設計和制造的微型加速度計,由于采用了微機電技術,其設計尺寸大大縮小,一個MEMS加速度計只有指甲蓋的一小部分,MEMS加速度計具有體積小、重量輕、能耗低等優點。

隨著微加速度計的應用越來越廣泛,對于微加速度計的數據信號采集和存儲變得極為重要。傳統的數據采集方法多數是用單片機完成的,其編程簡單、控制靈活,但缺點是控制周期長、速度慢,特別是對高速轉換的數據來說,單片機的慢速度極大地限制了數據傳輸速度。而FPGA(現場可編程門陣列)具有單片機無法比擬的優勢。FPGA時鐘頻率高,內部延時小,全部控制邏輯由硬件完成,速度快、效率高,適于大數據量的高速傳輸控制。在高速數據采集方面,FPGA有單片機無法比擬的優勢,然而單片機的接口豐富,數據處理能力強,便于完成數據的顯示和存儲等操作。

綜合單片機與FPGA的優點,這里介紹一種基于ARM和FPGA的微加速度計數據采集存儲系統,結合MXR6150G/M加速度計傳感器和TLC0820-A/D轉換芯片,提供了一種配置靈活、通用性強的數據采集方案。

1 系統整體設計方案

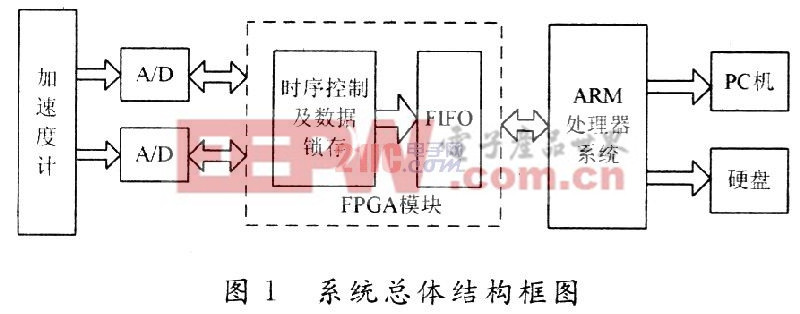

圖1是數據采集系統的總體結構框圖,該系統主要由雙軸加速度計、A/D轉換器、FPGA和ARM處理器四大部分組成。雙軸加速度計輸出兩路模擬信號,分別代表z軸與y軸的加速度值,通過A/D轉換芯片把輸入的兩路模擬信號轉換為8位的數字信號,FPGA接收來自A/D轉換芯片的數字信號,并對數字信號進行處理,處理后的數據經過FPGA中的FIFO存儲器緩存后由ARM處理器采取中斷方式接收采集,采集到的數據可以通過串口通信在PC機上實時顯示,也可以通過IDE接口存儲到大容量硬盤。

評論