NAND FLASH在儲存測試系統中的應用

圖3是從K9K8G08UOM存儲器中存入數據以后通過上位機軟件讀取的數據。經驗證,讀取的數據與往K9K8G08UOM存儲器中寫入的數據一致。

2 NAND FLASkI Memory的硬件部分

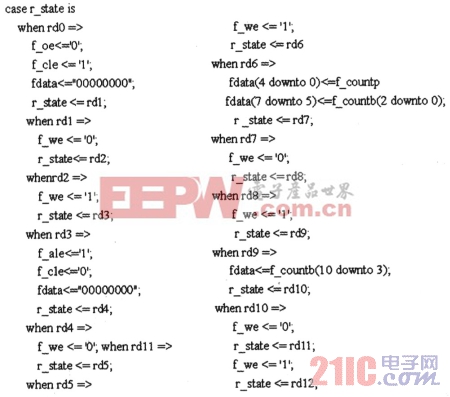

本設計當中,FLASH的數據輸入輸出口、控制端口通過調理電路與FPGA的端口相連,圖4所示是其硬件連接電路。

從圖4中可知,FLASH的數據輸入輸出端口I/00~7、控制端口/CE、是通過芯片SN54LV245與FPGA相連;FLASH的控制端口cLE、ALE、/WE、/RE通過芯片SN54LV245和芯片74HCl4與ITGA相連。其中F-CLE、F-ALE、F—WE、F-RE、F—CE、F-R/Bur是FPGA的I/O口,是FPGA邏輯的輸入輸出口。CLE、ALE信號是FLASH存儲器命令、地址鎖存使能信號,/WE是保證命令、地址、數據能否及時正確的寫入FLASH的信號,/RE信號控制著數據的讀取,這些信號的精確度關系著FLASH存儲、讀數功能的實現。所以,這些信號的好壞直接關系著FLASH的正常工作。經實踐的電路調試,這些信號在傳輸過程中受到了其它因素的干擾,信號明顯失真,在電路中加入74HCl4(非門)以后,信號會變得光滑,準確。

芯片SN54LV245是八進制三態總線收發器,DIR=1時,總線傳輸方向從A→B;DIR=0時,總線傳輸方向從B→A。/OE是片選信號。/0E,DIR信號是由FPGA內部編程邏輯控制的。

FL,ASH接口中,為了保證/wE、/RE、/CE、R/B控制信號初始狀態無效,由硬件電路實現端口值拉高。本設計中不使用寫保護功能,所以/WP端口也接上了上拉電阻。

3 結束語

基于閃存技術的固態存儲器存儲密度大,功耗小,可靠性高,體積小重量輕且成本也在不斷降f氐,在航空應用中有良好的應用前景。在設計儲存測試系統時選用大容量的NAIXD FLASH存儲器大大提高了儲存、讀取速度,并且設計電路結構簡單,易于修改。

評論