FPGA深層解析

請查看下方白皮書的對策列表,獲取更多Virtex-5 FPGA相關信息。

乘數器和DSP片

圖13.乘數器功能

看起來簡單的兩數相乘運算在數字電路中實現起來是十分復雜的,也是極為消耗資源的。為提供相關參考,圖14所示是一種使用組合邏輯電路實現4×4字節乘數器的示意圖。

圖14.兩個4字節輸入相乘的電路圖

試想兩個32字節的數字相乘要通過2000多步操作才能得到結果。因此,FPGA預設了乘數器電路,在數學和信號處理應用中保存對查找表和觸發器使用。Virtex-II和Spartan-3 FPGA擁有18×18bit乘法器,所以兩個32字節數字相乘的運算需要三個乘法器來實現。許多信號處理算法都包括連乘運算結果的功能,因此Virtex-5等高性能FPGA都預設被稱為DSP片的乘數器累加電路.這些預設處理組件,也被稱為DSP48片,包括25×18bit乘數器以及加法器電路,盡管您可單獨使用乘數器功能。表5所示為不同FPGA系列DSP決策。

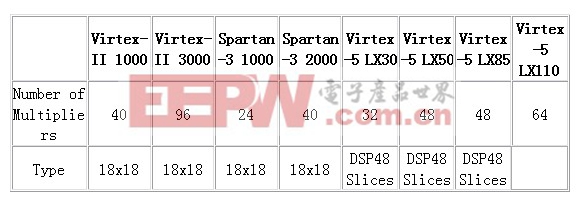

表5.不同FPGA的DSP源

塊隨機存取存儲器(RAM)

選擇FPGA時,記憶源是另一個需要考慮的關鍵因素。嵌入FPGA芯片中的用戶自定義隨機存取存儲器(RAM),對儲存數據設置或平行環路之間傳送數值很有幫助。基于FPGA系列,您可在16或36kb組件中設置板載RAM,或者使用觸發器以數組來執行數據設置;然而,對于FPGA邏輯源來說,大型數組很快就變得十分“奢侈”。由100個32字節元素數組可消耗Virtex-II 1000 FPGA中超過30%的觸發器,或者占用少于1%的嵌入式塊RAM。DSP算法通常需要追蹤整個數據塊或是復雜等式的系數,而在沒有板載存儲器情況下,許多處理功能在FPGA芯片的硬件邏輯電路中都不適用。圖16所示為使用塊RAM讀寫存儲器的圖形化功能。

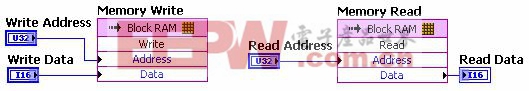

圖15.用于讀寫存儲器的塊RAM函數

同樣,你也可以使用內存塊,將一段完整周期存儲為數值和索引的順序表,為板載信號發生器存儲周期性波形數據。輸出信號的最終頻率由檢索數值的速度決定,這樣您就可用此方法動態改變輸出頻率,而不需要輸入波形中的急劇變化。

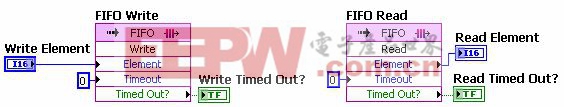

圖16.用于先進先出緩沖器的塊RAM功能

FPGA固有的并行執行要求邏輯電路獨立元件可在不用時間脈沖下驅動。在不同運行速度下的邏輯電路之間傳遞數據是很棘手的。使用先進先出(FIFO)緩沖器時,板載存儲器可用來是傳輸更加平穩。如圖16所示,用戶可以將FIFO緩沖器配置成不同大小以確保數據在FPGA芯片的非同步部件間不會丟失。表6所示為嵌入不同FPGA系列的用戶可設置快RAM。

表6.不同FPGA的記憶源

總結

隨著高端技術的發展以及新概念的深入概括,FPGA技術地采用將不斷增加。然而探究FPGA其中奧秘,感嘆這硅片中在方框圖間匯編出的變化,也是十分重要的。在發展階段,如果您懂得如何利用和優化資源,比較和選擇觸發器、查找表、乘數器和塊RAM等硬件指標是十分有幫助的。這些基本的功能塊并不是包含所有資源的完整清單,而且這篇白皮書并沒有包含對所有FPGA部件的討論。用戶可以通過下面的推薦資源,繼續學習關于FPGA和數字硬件設計的知識。

評論