FPGA深層解析

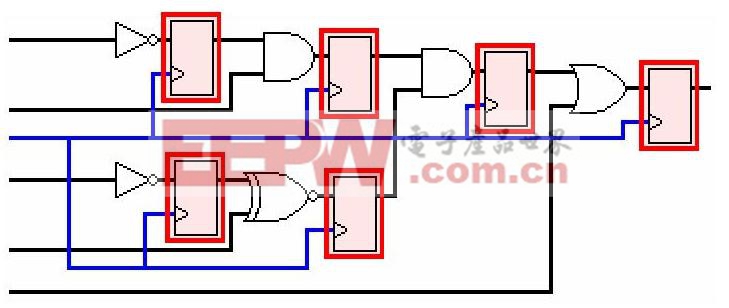

觸發(fā)器是二進制移位寄存器,用于同步邏輯以及保存時鐘(脈沖)周期內(nèi)的邏輯狀態(tài)。在每個時間(脈沖)邊沿,觸發(fā)器在輸入時鎖定1(真)或0(假)值并且保存此值直到下次時鐘(脈沖)邊沿。在正常情況下,LabVIEW FPGA在每次操作之間都設置一個觸發(fā)器,以保證有足夠的時間來執(zhí)行每步操作。對此律的例外只發(fā)生在SCTL結構中寫代碼的情況。在這個特殊的環(huán)路結構中,觸發(fā)器只放置在閉環(huán)迭代的始末段,并且由編程者考慮定時因素來決定如何放置。對SCTL內(nèi)代碼如何同步的更多內(nèi)容將在以后章節(jié)中討論。圖5表示的是圖3的上端分支,觸發(fā)器由紅色高亮表示。

圖5.繪制由紅色高亮表示出觸發(fā)器的電路圖

查找表

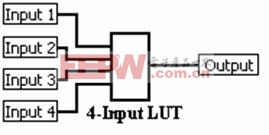

圖6.雙四輸入查找表

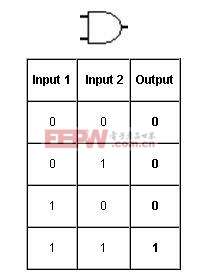

圖6所示示意圖中的其他邏輯電路通過使用少量查找表形式的隨機存取存儲器實現(xiàn)。我們可以簡單地假定FPGA中系統(tǒng)門的數(shù)量可參考與非門(NAND)以及或非門(NOR)的數(shù)量,但實際上,所有的組合邏輯(與門、或門、與非門、異或門等)都是通過查找表存儲器中的真值表來實現(xiàn)。真值表是輸出對應于每個輸入值組合的預定義表(現(xiàn)在卡諾圖的重要性在你的頭腦中可能會慢慢淡化)。以下是對數(shù)字邏輯電路課程的快速回顧:比如,圖7是布爾邏輯與門操作過程。

這是對數(shù)字邏輯課程的快速回顧:

例如,圖7中顯示了布爾型AND操作。

圖7.布爾型AND操作

表2.布爾與門操作的真值表

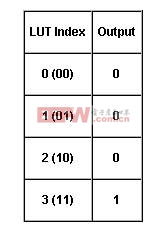

你可以認為輸入值是所有輸出值的數(shù)字索引,如表3所示。

表3.布爾與門擦操作的真值查找表實現(xiàn)

Virtex-II和Spartan-3系列FPGA芯片有著4輸入查找表來實現(xiàn)真正的4輸入信號的16種組合。圖8就是一個四輸入電路實現(xiàn)的例子。

圖8.輸入布爾邏輯的四信號電路

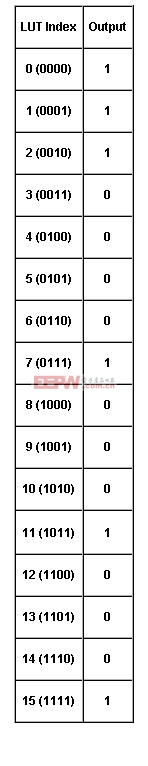

表4所示為使用雙四輸入查找表實現(xiàn)的相應的真值表。

表4.圖8中所示相應真值表

Virtex-5系列的FPGA使用雙六輸入查找表,可以通過6個不同輸入信號的64種組合來實現(xiàn)真值表。因為觸發(fā)器之間的組合邏輯十分復雜,所以在LabVIEW FPGA中使用SCTL也越來越重要。下一節(jié)將講述SCTL如何優(yōu)化利用LabVIEW中的FPGA源。

評論