FPGA深層解析

SCTL

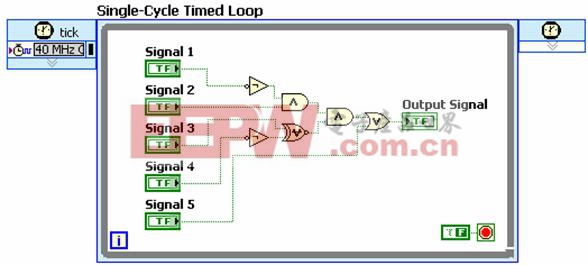

上幾節中使用的代碼例子假定代碼是設置在SCTL外部,并為保證執行同步數據量也同步了附加電路。SCTL是LabVIEW FPGA中一個特殊結構,生成一個更為優化的電路圖,以期望達到在一個時鐘(脈沖)周期內執行完所有邏輯電路分支。例如,若設置SCTL在40MHZ運行,則所有邏輯電路分支將在25ns內執行完畢。

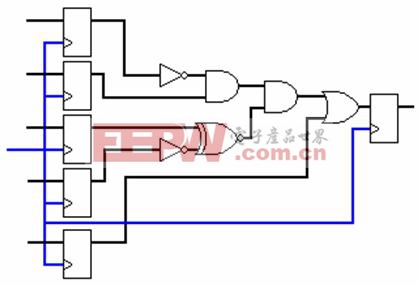

如果在SCTL中設置前例中同樣的布爾邏輯電路(如圖9所示),則生成如圖10所示的相應電路示意圖。

圖9.附有STCL的簡單布爾邏輯

圖10.圖9所示布爾邏輯相應的電路圖

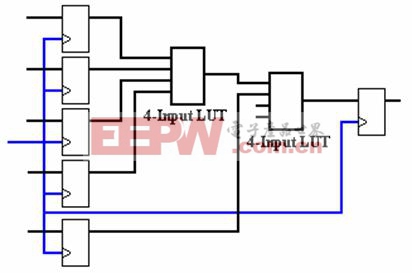

很明顯,這種實現方法簡單多了。在Virtex-II或Spartan-3系列FPGA中,觸發器間的邏輯需要至少2個4輸入查找表,如圖11所示。

圖11.圖10中電路圖的雙四輸入查找表實現

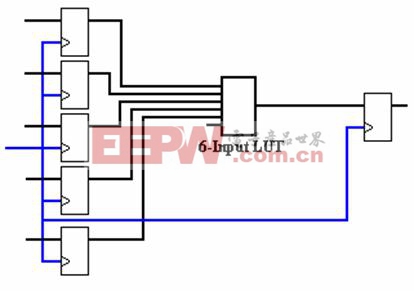

由于Virtex-5系列FPGA有著6輸入的查找表,用戶可以在一個查找表中實現相同數量的邏輯,如圖12所示。

圖12.圖10中雙六輸入查找表實

本例中使用的SCTL(如圖9所示)設置在40MHZ下運行,這意味著在任意觸發器之間邏輯電路必須在25ns內完成執行。電子在電路中傳播的速度決定了代碼執行的最大速度。關鍵路線是有最長傳播延遲的邏輯電路分支,它決定了該部分電路中理論最大時鐘速率。Virtex-5 FPGA上的雙六輸入查找表不僅減少實現給定邏輯電路所需要的查找表總數,而且減少電子通過邏輯電路的傳播延遲(時間)。Virtex-5系列FPGA中的6輸入查找表不僅可以減少實現特定邏輯而需要的查找表的數量,而且可以降低邏輯中電流的傳輸延時。這意味著,您可簡單地通過選擇一個基于Virtex-5的硬件指標設置相同的SCTL,追求更快的時間速度。

評論