基于SOPC的低電壓電泳芯片系統平臺設計

如圖1所示,在一片CyclonII 2C35 FPGA中,采用SOPC Builder構建主從雙CPU架構的系統,其中CPU1作主控,負責電泳信號的數據采集、處理及任務分配;CPU2作協處理,負責低電壓電泳芯片進樣控制電路、分離電壓控制。主控CPU1采集電泳信號后,將部分數據,如是進樣還是分離、是否結束、電壓是否施加到下一電極對等標志發送給從CPU2處理, 然后由CPU2再控制相應地控制電路,最終實現電極施加電壓位置與待分離組分運動范圍保持一致。這種結構由于CPU1和CPU2各自控制一部分電路模塊,且主、從CPU交換的數據較少,有利于保障整個系統的高速采集與控制處理。主從CPU之間數據交換通過內嵌的雙口RAM來實現。若主、從CPU數據交換多且頻繁,一般不采用此種主從結構[6-7],可采用流水線結構,無論怎樣的架構,系統都可在不改變硬件的條件下,通過軟件更新就可實現雙CPU架構的改變。

4 系統軟件的設計

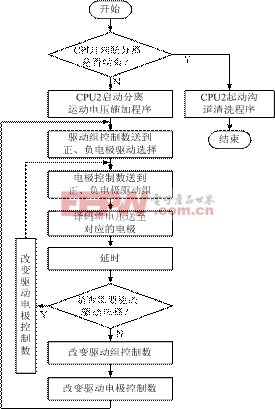

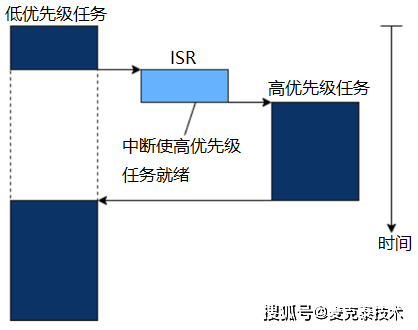

本系統的軟件設計,主要包括:基于SOPC Builder定制的低電壓運動控制模塊設計,基于Avalon流模式電泳信號采集IP核設計,負壓進樣控制模塊設計、片上系統集成開發軟件設計、片上系統與PC機之間的通訊設計以及上位機電泳譜分析分析軟件等組成。其中,上位機開發軟件為C++ Builder。由于篇幅有限,本文僅給出低電壓運動控制控制流程圖以及毛細管電泳芯片采集與控制軟件結構圖,分別見圖5,圖6所示。

圖5 低電壓運動控制流程圖

圖6 毛細管電泳芯片采集與控制軟件結構圖

5 結 論

本文提出了一種基于SOPC的低電壓毛細管電泳芯片采集與控制的實現方法。通過在Altera的CyclonII FPGA中利用SOPC Builder庫中的NiosII軟核處理器,基本IP核以及自定制IP核,能靈活快速地搭建真正意義上屬于自己的采集與控制SOPC系統,縮短開發周期;通過內嵌于FPGA內部的NIOSII軟核處理器,能靈活方便地實現多處理器并行處理結構,保證系統高速處理;采用單芯片實現片上系統使系統解決方案更可靠、更廉價、更簡潔;通過定制指令,利用FPGA多個并行處理單元, 使得在某些方面的處理能力大大超過硬核處理器,如DSP處理器;該方案由于采用SOPC技術能通過軟件的不斷更新實現系統硬件以及軟件的升級與換代。

本文作者的創新點:將SOPC技術應用于生物芯片的控制與檢測,在硬件不變的條件下,通過軟件更新就可對整個系統進行升級換代,特別適合生物芯片技術前期開發以及探索性研究。

評論