基于DDS技術的多路同步信號源的設計

摘 要:多路同步數字調相信號源一般采用單片機和多片專用DDS芯片配合實現。該技術同步實現復雜,成本高。給出了一種基于FPGA的多路同步信號源的設計方法,通過VHDL語言硬件編程實現了基于單片FPGA的多路同步信號,數字調相快速準確。利用QuartusⅡ進行綜合和仿真驗證了該設計的正確性,該設計具有調相方便、速度快、成本低等優點。

關鍵詞:DDS;多路同步;VHDL;FPGA

引 言

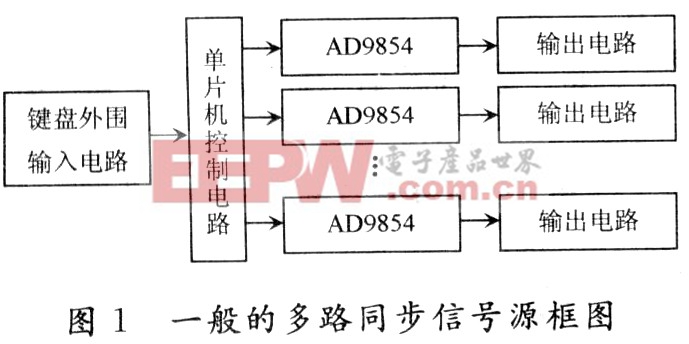

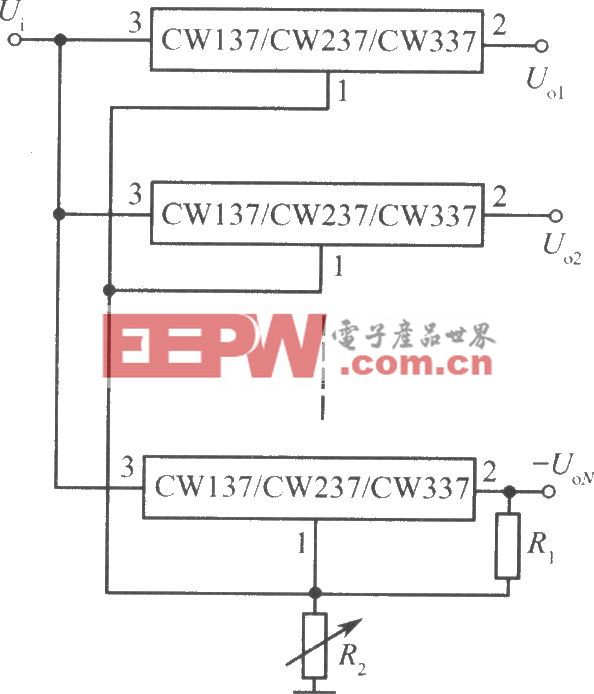

實現信號源的多路同步輸出,在雷達、通信等多領域有著重要的應用。為了實現此功能,大多數設計是利用多個專用DDS芯片外圍借助單片機幫助,實現多信號同步輸出,如圖1所示。

系統工作時,根據鍵盤輸入,單片機輸出頻率控制字和相位控制字以及波形選擇字,控制專用DDS芯片AD9854產生特定頻率和相位的波形,經濾波放大后輸出要求的模擬波形。為輸出頻率相同,相位相關的多路同步信號,控制數據由鍵盤輸入,單片機向各專用DDS芯片輸出相同的頻率控制字和不同的相位控制字指令,控制各專用DDS芯片輸出指定的頻率和相位的波形。這樣就從整體上實現了頻率和相位的連續可調及同步。

AD9854是美國AD公司的DDS系列產品,性能良好,頻率可調范圍寬。在這樣的設計中,利用AD公司的AD9854芯片,盡管有頻率可調范圍寬,波形豐富,實現調副、調頻容易等特點,但是由于是采用分立的專用DDS芯片,各芯片參數很難做到完全相同,參數的差異會造成輸出信號頻率和相位不同。因此,盡管各DDS芯片采用同一頻率字,各個輸出信號頻率也難以完全相同。同樣,由于參數的不一致,波形之間的相位也難以準確調整到位,更重要的是各個信號頻率差異的累積效應可能會導致同步失敗。另外,專用DDS芯片價格昂貴,設計成本也較高。

基于以上原因,這里給出一種基于單片FPGA的多路同步信號源的設計方案,這種方案具有實現簡單、同步性好等優點,且成本較低。

1 基于FPGA技術的多路同步信號源的設計模型

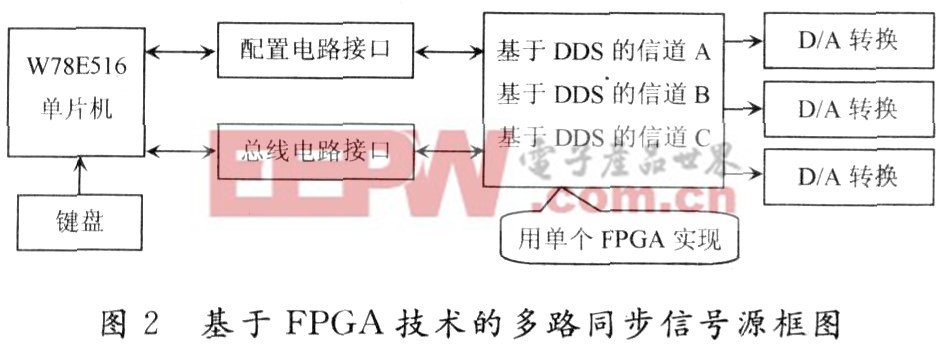

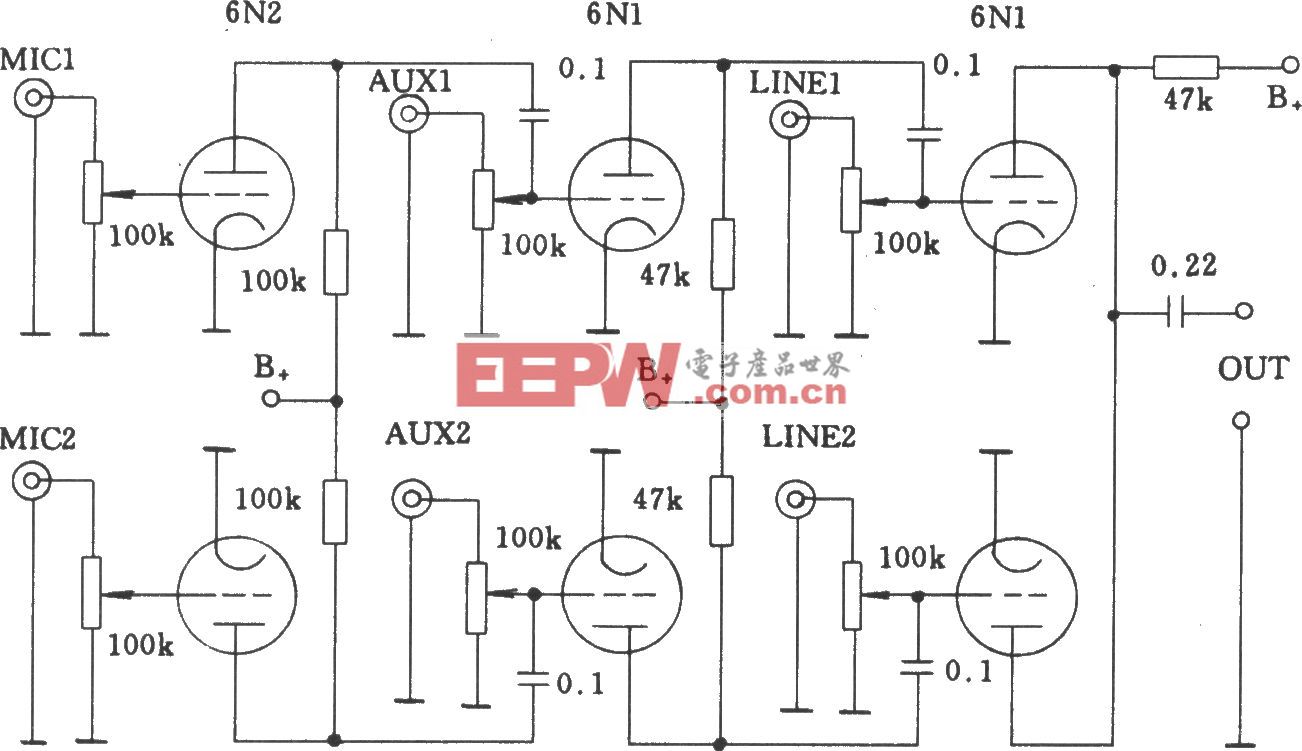

基于FPGA技術的多路同步信號源的整體框圖如圖2所示。

在本框圖中,以三路輸出為例,在一個FPGA芯片中,實現了三路基于DDs的信號通道,完成傳統上三個專用DDS芯片AD9854完成的功能,實現三路波形的數字輸出,在數字信號輸出后進行D/A轉換,實現三路信號的模擬輸出。三個DDS信道頻率取自同一個累加器輸出的地址值,進行查表,同時相位的加法實現也是針對同一個累加器輸出的地址,消除了分立專用DDS芯片計算的誤差。由于在一塊芯片中實現,所以各DDS信道的參數一致性好,分立專用DDS芯片的外部連線帶來的延時誤差也被降到最低。因此,通過以上措施,可以大大改善信號的一致性,可實現精準的相位連續調節。

評論