用低成本FPGA解決高速存儲(chǔ)器接口挑戰(zhàn)

實(shí)現(xiàn)高性能的DDR存儲(chǔ)器需要在輸入端的讀操作和在輸出端的寫操作有專用的DDR寄存器結(jié)構(gòu),LatticeEC提供這個(gè)能力。除這些寄存器外,EC器件有兩個(gè)單元簡(jiǎn)化用于讀操作的輸入結(jié)構(gòu)設(shè)計(jì),這兩個(gè)單元是DQS延時(shí)塊和極性控制邏輯。這兩個(gè)塊對(duì)于實(shí)現(xiàn)可靠的高速DDR SDRAM控制器十分關(guān)鍵。由于DQS邏輯的復(fù)雜性,用FPGA實(shí)現(xiàn)高速存儲(chǔ)器控制器時(shí),設(shè)計(jì)者會(huì)遇到問(wèn)題。LatticeEC為設(shè)計(jì)者提供這些專用塊,能夠緩解這個(gè)問(wèn)題。

DLL校準(zhǔn)DQS延時(shí)塊

源同步接口通常要求調(diào)整輸入時(shí)鐘,以便用輸入寄存器正確捕獲數(shù)據(jù)。對(duì)大多數(shù)接口而言,PLL被用于這種調(diào)整。然而對(duì)于DDR存儲(chǔ)器,稱為DQS的時(shí)鐘是受約束的,因此這種方法不可行。在DDR存儲(chǔ)器接口,DQS與主時(shí)鐘的關(guān)系會(huì)有變化,這是由于PCB上走線的長(zhǎng)度和使用的存儲(chǔ)器所引起的。

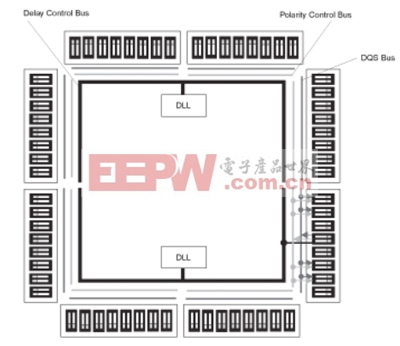

圖3:DLL校準(zhǔn)總線和DQS/DQS轉(zhuǎn)移分布。

如圖2所示,Lattice DQS電路包括一個(gè)自動(dòng)時(shí)鐘轉(zhuǎn)移電路,用以簡(jiǎn)化存儲(chǔ)器接口設(shè)計(jì)和保證穩(wěn)健的操作。此外,DQS延時(shí)塊還提供用于DDR存儲(chǔ)器接口所需的時(shí)鐘對(duì)列。來(lái)自焊盤的DQS信號(hào)通過(guò)DQS延時(shí)單元送入專用的布線資源。DQS信號(hào)也送入極性控制邏輯,用于控制輸入寄存器塊中連至同步寄存器的時(shí)鐘極性。

專用DQS延時(shí)塊的溫度、電壓和工藝變化由一組校準(zhǔn)信號(hào)(6位寬的總線)進(jìn)行補(bǔ)償,它們來(lái)自器件兩側(cè)的兩個(gè)DLL。每個(gè)DLL補(bǔ)償器件一半的DQS延時(shí),如圖3所示。DLL用系統(tǒng)時(shí)鐘和專用反饋環(huán)來(lái)補(bǔ)償。這是一個(gè)重要的結(jié)構(gòu)特征,因?yàn)檫@個(gè)器件不會(huì)受到通常其它FPGA嚴(yán)格的I/O布局要求的牽制。

極性控制邏輯

對(duì)于典型的DDR存儲(chǔ)器設(shè)計(jì),延時(shí)DQS選通脈沖和內(nèi)部系統(tǒng)時(shí)鐘(在讀周期)之間的相位關(guān)系是未知的。Lattice-EC器件含有專用電路在這些域間傳遞數(shù)據(jù)。為了防止建立和保持時(shí)間發(fā)生變化,即DQS延時(shí)和系統(tǒng)時(shí)鐘間的域傳遞,它使用了一個(gè)時(shí)鐘極性選擇器,這改變了鎖存在輸入寄存器塊中同步寄存器中的數(shù)據(jù)的邊沿。這需要測(cè)定在每個(gè)讀周期的起始時(shí)刻有正確的時(shí)鐘極性。DDR存儲(chǔ)器讀操作前, DQS處于三態(tài)(由端接上拉)。起始時(shí)刻DDR存儲(chǔ)器驅(qū)動(dòng)DQS為低電平,一個(gè)專用電路用于檢測(cè)這個(gè)傳遞,這個(gè)信號(hào)用來(lái)控制至同步寄存器的時(shí)鐘極性。

評(píng)論