用低成本FPGA解決高速存儲器接口挑戰

由于線路速率繼續增長,DDR SDRAM在網絡應用中正在被廣泛地采用。不斷增加的系統帶寬要求正在推動存儲器接口速度提高,而成本仍不斷壓低。LatticeEC FPGA系列的專門而靈活的DDR能力使設計者擁有滿足下一代存儲器控制器需求的低成本解決方案。

本文引用地址:http://www.104case.com/article/192026.htm存儲器已廣泛地應用于當今的電子系統。由于系統帶寬的不斷增加,存儲器技術針對更高的速度和性能進行了優化。結果,下一代存儲器接口的設計變得越來越具有挑戰性。在諸如FPGA的可編程器件中實現高速、高效的存儲器接口對于設計者來說一直是一個主要的挑戰。以往,只有少數FPGA??持能可靠地與下一代高速器件接口的構建模塊,這些FPGA通常是高端的昂貴器件。不過,現在LatticeEC FPGA系列也提供在低成本FPGA結構中實現下一代DDR2、QDR2以及RLDRAM控制器所需的構建模塊、高速FPGA結構、時鐘管理資源和I/O結構。

存儲器應用

存儲器是各種系統的組成部份之一,不同的應用有不同的存儲器要求。對于網絡基礎設施應用,所需的存儲器通常為高密度、高性能和高帶寬,并具有高可靠性;在無線應用中,特別是手機和移動設備,低功率存儲器是很重要的;而對于基站應用,高性能很關鍵。寬帶應用要求存儲器在成本和性能方面有很好的平衡;計算與消費類應用則需要諸如DRAM模塊、閃存卡和其它對成本很敏感的存儲器解決方案,同時要滿足這些應用的性能目標。本文主要討論在網絡和通信中的存儲器應用。

網絡和通信應用需要大的、快速存儲器,完成從小的地址查找到流量修整/監控再到緩沖器管理等各種任務。用于消費應用的價格便宜、成熟的FMP和EDO DRAM通常不適用,因為它采用了較慢的異步方式,且需要時序精確的命令信號來初始化數據轉移。網絡系統架構師一般轉向采用靜態RAM,解決時延問題,但這導致較高的成本。通過去除讀和寫周期間的等待狀態和空閑周期,ZBT SRAM被廣泛地用于改進存儲器帶寬。

最近,系統架構師在網絡基礎設施應用中轉向使用SDRAM,以便減少時延、滿足低成本要求。上述任務的每一個都伴隨一組獨特的需求。例如,低的和中等帶寬的應用要求低時延的存儲器,因此ZBT SRAM是理想的。

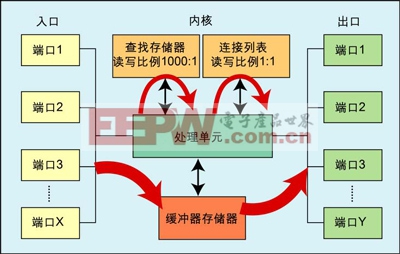

圖1:網絡中的存儲器。不同的功能需要不同的方法。

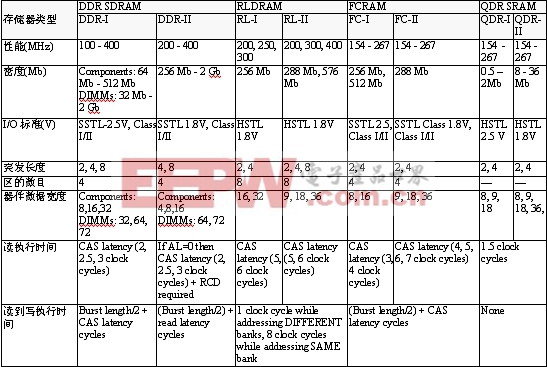

表1:為用于高速網絡應用的存儲器綜合比較。

評論