用低成本FPGA解決高速存儲器接口挑戰

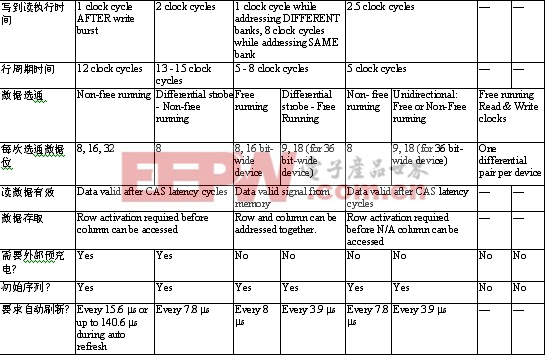

圖1顯示了典型的網絡架構。在10Gbps,一個讀寫比為1000:1的地址查找可很容易地在DDR SRAM中得到處理。連接列表管理、流量修整、統計收集任務通常具有平衡的1:1讀寫比,需要較高性能的QDR SRAM。另一方面,較大的緩沖存儲器一般在DDR SDRAM中實現。作為DRAM的替代,SDRAM同步存儲器訪問的處理器時鐘用于快速數據傳輸。達到快速是因為SDRAM允許存儲器的一個塊被存取,而另一個塊準備被存取。與DRAM不同,SDRAM采用流動電流而不是存儲電荷,除去了連續刷新的需要。

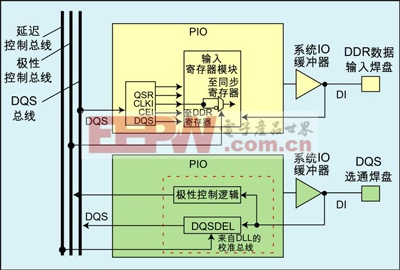

圖2:LatticeEC FPGA中的專用DQS電路。

兩個新的競爭者進入了高精度存儲器舞臺。快速周期隨機存取存儲器(FCRAM)改進了性能,它采用了流水線操作和隱蔽的預充電技術以減少隨機存取周期時間,高度分段的存儲器核減少了功耗。存儲器核分段為較小的陣列,這樣數據可以被很快地存取并改進執行時間。這些特征使得FCRAM被理想地用作緩沖存儲器,用于諸如交換、路由和網絡服務器等的高速網絡應用中。時延減少的DRAM(RLDRAM)提供SRAM類型的接口以及非多路復用的尋址。RLDRAM II技術提供最小時延并可減少行周期時間,這些特征很適用于要求關鍵響應時間和快速隨機存取的應用,例如下一代10Gbps以及更加高速的網絡應用。

存儲器控制器的挑戰

目前存儲器接口經常要求時鐘速度超過200MHz以滿足線卡和交換卡的吞吐量要求,這是FPGA架構的主要挑戰。PLL是基本的允許控制時鐘數據關系的部件。

下一代存儲器控制器工作在HSTL或SSTL電壓。低電壓電平的擺動是需要的,以便??持存儲器和存儲器控制器的輸入輸出的高速數據操作。對于高速SRAM存儲器來說,HSTL是實際的I/O標準,而對于高速DDR SRAM存儲器,SSTL是實際的I/O標準。

高速差分I/O緩沖器和專用電路的組合能夠在高帶寬下進行無縫讀寫操作,傳統上這屬于高級FPGA的領域。LatticeEC FPGA改變了那個慣例,通過低成本FPGA架構實現了高帶寬存儲器控制器。

表1:為用于高速網絡應用的存儲器綜合比較。

DDR存儲器控制器的支持

評論