基于FPGA技術實現與PC串行通信

摘要:本文主要介紹了基于FPGA技術實現與PC串行通信的過程,給出了各個模塊的具體實現方法,分析了實現結果,驗證了串行通信的正確性。

本文引用地址:http://www.104case.com/article/192024.htm引言

串行通信即串行數據傳輸,實現FPGA與PC的串行通信在實際中,特別是在FPGA的調試中有著很重要的應用。調試過程一般是先進行軟件編程仿真,然后將程序下載到芯片中驗證設計的正確性,目前還沒有更好的工具可以在下載后實時地對FPGA的工作情況和數據進行分析。通過串行通信,可以向FPGA發控制命令讓其執行相應的操作,同時把需要的數據通過串口發到PC上進行相應的數據處理和分析,以此來判斷FPGA是否按設計要求工作。這樣給FPGA的調試帶來了很大方便,在不需要DSP等其他額外的硬件條件下,只通過串口就可以完成對FPGA的調試。本文采用QuartusⅡ3.0開發平臺,使用Altera公司的FPGA,設計實現了與PC的串行通信。

總體設計

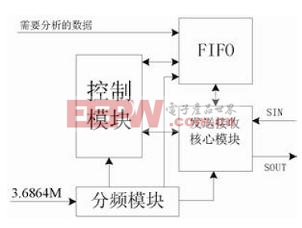

主要設計思想:PC向串口發送命令,FPGA通過判斷接收的控制字執行相應的操作,總體框圖如圖1所示。

圖1 總體框圖

設計包括三部分:1、通過向I/O端口發送高低電平以達到控制外部硬件的要求。2、完成芯片內部邏輯的變化。3、將需要的數據先存起來(一般采用內部或外部FIFO),然后通過串口將數據發送到PC,PC將接收的數據進行處理和分析。串口采用標準的RS-232協議,主要參數的選擇:波特率28800bit/s、8位有效位、無奇偶校驗位、1位停止位。

FPGA中各模塊的實現

分頻模塊

設計中需要將3.6864MHz的時鐘進行64分頻變為57600 波特作為其他模塊的時鐘基準。具體實現時采用一個6位計數器,將計數器的溢出作為時鐘的輸出即可實現整數分頻。

發送接收模塊

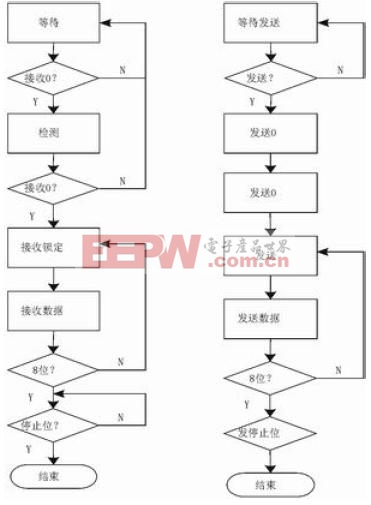

此模塊是整個設計的核心部分。設計流程如圖2所示。

圖2 發送接收流程圖

在串行通信中,無論發送或接收,都必須有時鐘脈沖信號對所傳送的數據進行定位和同步控制,設計中采用的時鐘頻率是波特率的兩倍(57600 bit/s)。接收過程:初始狀態是等待狀態,當檢測到0時進入檢驗狀態,在檢驗狀態下如果再檢測到0則進入接收數據狀態,當接收完8位比特數后判斷是否有停止位,如果有則結束接收過程重新進入等待狀態。發送過程:初始狀態是等待狀態,當接收到開始發送的信號則進入發送過程,先發送起始位,再發送8位比特數,每位寬度為2個周期,當一個字節發送完畢后發送一個停止位,發送結束,重新回到等待狀態。

評論