20×18位符號定點乘法器的FPGA實現

SMIC提供的0.18 vm標準單元庫中,4-2壓縮CMPR42的邏輯表達式為:

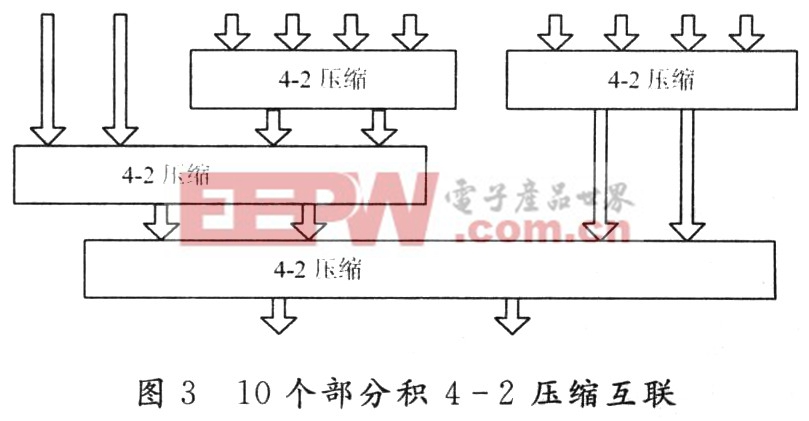

在硬件實現該模塊時,因為有10個部分積,一共調用4-2壓縮4次,分為3級,從頂到底為2―1―1型。4-2壓縮互聯如圖3所示。

1.3 溢出處理及四舍五入

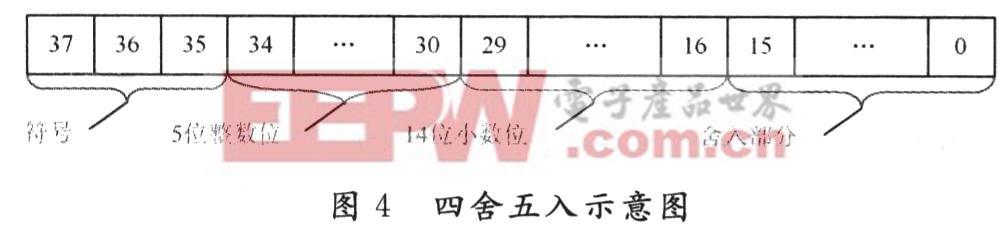

定點數相乘不會溢出,只不過結果的最終位數有所增加。20 b×18 b結果為38 b。有時38 b并不全部存儲,只需其中的一些位就可以。這涉及到四舍五人。假設數A共20位,1位符號,5位整數位,14位小數位,數B共18位,1位符號位,2位整數位,15位小數位,結果格式同A。

如圖4所示,因為只保留5位整數,把前3位都看成是符號位,如果不同,說明溢出;反之,沒溢出。再根據前兩位真正的符號判斷是上溢還是下溢,若為O,則上溢,為20'h7ffff,反之,下溢,為20'h80001。在邏輯設計上用個選通可以實現,Verilog HDL代碼為:assignceil=data in[37]:20'h80001:20'h7ffff;其中data in[37]為最高位。

由于Verilog HDL語言是應用最為廣泛的硬件描述語言之一,可以進行各種層次的邏輯設計,也可以進行仿真驗證,時序分析,并且可移植到不同產家的不同芯片中,代碼可讀性比較強,因此本模塊設計用Ver-ilog HDL語言。

如果要舍入的數沒有溢出,那么還要考慮小數部分的舍入。若舍入數為正數,舍入相鄰位為1,舍入時必須進1;反之不用。若舍人數為負數,舍入相鄰位為1且舍人相鄰位后面還有一位為1,則舍入時需加1;反之,不加1。

評論