FPGA和EZ-USB FX2在采集圖像數據中的應用

摘 要:利用FPGA和EZ_15SB FX2(CY7C68013)將MT9M112(Sensor)數據準確無損地傳給PC機。方案使用CY7C68013控制器工作在Slave FIFO從機方式,用Verilog HDL語言在FPGA中產生相應的控制信號,最終實現對數據的快速傳輸,在上位機得到Sensor采集的清晰畫面。該方案的傳輸速度快,數據準確,可擴展到其他需要通過USB進行快速數據傳輸的系統。與其他采用異步通信方案相比,設計利用FPGA緩沖作用,使數據無丟失傳輸,最終在上位機得到的圖像更加清晰流暢。該設計方案和產品達到國際先進水平。

關鍵詞:同步傳輸;異步傳輸;數據流;FIFO_Core;slave FIFO

由于一維碼、二維碼以及圖像掃描處理等方面都涉及到了PC機和下位機間的數據傳輸,而傳輸數據阻塞問題又是制約圖像效果的根本原因,該方案很好地解決了這個問題。設計采用美光的CMOS圖像傳感芯片MT9M112作為圖像采集部分,通過EZ_USB。FX2的USB微控制器芯片68013a將采集到的數據傳送到PC機,由PC機對二維碼圖像進行顯示并做解碼處理。由于MT9M112輸出的是8位的串行圖像數據流,直接與68013a的從FIFO接口對接不能保證數據完整不丟失,并且無法在數據中加入幀識別信息。在這種情況下采用了FPGA完成此部分邏輯功能。通過FPGA對圖像數據做相應的調整再交給68013a傳送到上位機。

1 詳細設計方案及性能分析

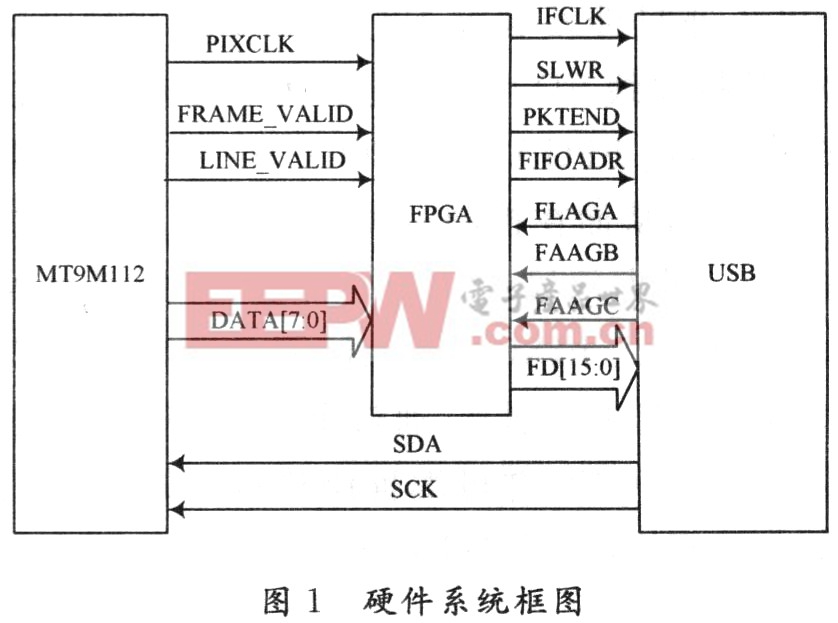

1.1 硬件系統框圖

硬件系統框圖如圖1所示,實現了各模塊數據信號和控制信號的鏈接。

1.2 Sensor輸出部分說明

MT9M112的輸出具有以下的特性:MT9M112內部有一個PLL鎖相環,通過相應的寄存器設置可調整輸出數據的同步時鐘,默認輸出ITU_R BT.656(YCbCr)格式的數據流。LINE_VALlD指示一個行有效數據輸出周期,FRAME_VALID指示一個幀輸出周期,在幀和行同時有效時以像素時鐘PIXCLK為基準輸出8位的圖像數據,根據時序,只要行有效為高,輸出總線有圖像數據,這樣就可以將FPGA的寫是能改為高有效(默認低有效),直接將行有效信號連接到寫使能管腳,從而控制向FPGA FIFO的寫。

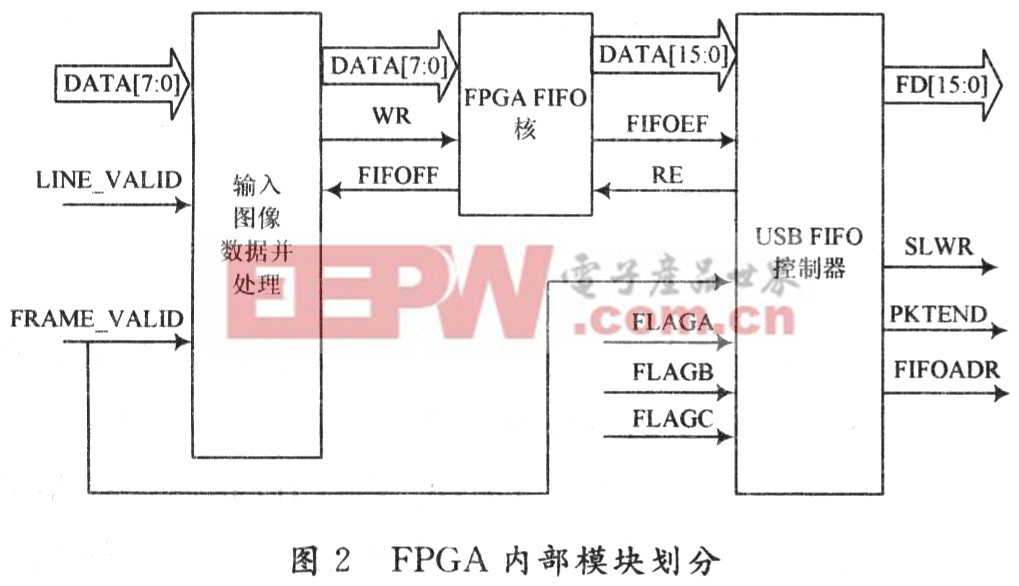

1.3 FPGA內部模塊及主要原理

在FPGA開發工具中創建F1FO_Core,設置其輸入數據位寬為8 b格式,輸出數據寬度為16 b格式,目的是在控制時鐘不變的情況下加快傳輸數據速率。時鐘選為single clock,即FPGA FIFO核的讀和向USB FIFO的寫用同一時鐘.PIXCLK,同時利用Verilog HDI,語言實現其內部模塊互連。脫機解碼時上位機程序為了識別一個有效的幀數據段,在下位機傳遞數據時,在每幀圖像數據間插入了16 B的同步數據(該數據可由工作人員決定),以鑒別一幀圖像開始。設計將同步數據中將同步信息分為4個4 B數據。第一個數據為同步頭,向上位機發數據固定為0xAA550000,第二個數據表示圖像的比例,高字節為行,低字節為列。第三以及第四個數據為保留字目前為O。FPGA除負責傳輸有效的幀圖像外還要在兩個圖像幀數據之間插入同步數據。是在FRAME_VALID的下降沿到來后(即一幀數據傳輸結束后發同步信息)并且FPGA的FIFO empty_flag有效時發送,以此來判斷下一幀數據的開始,FPGA FIFO核與USB及圖像數據關系如圖2所示。

1.4 68013a從FIFO接口

Sensor采集的數據經過FPGA做處理寫到EZ_LISB FX2 68013A的從FIFO,由EZ_USB FX2 68013A將數據打包放送到上位機。由于上位機的數據同步為固定的同步信息,不涉及到FPGA回讀上位機數據部分,所以此處只涉及到寫EZ_USB FX2 68013A的從FIFO。數據總線FD可編程選擇為8位或是16位的位寬(該方案通過FPGA的FIFO_Core將總線數據轉換為16位格式,從而在控制時鐘不變的情況下加快傳輸數據速率),同步傳輸時鐘由外部提供時,通過外部對IFCLK引腳引入PIXCLK時鐘(同步電路)。EZ_USBFX2 68013A有4個端點,通過FIFOADR設置選擇數據總線與EP6對應,并可編程調整對應的FIFO深度。通過固件編程可將FLAGA,FLAGB,FLAGC調整為對應哪個內部FIFO的對應滿空狀態。PKT、END用于手動打包傳輸數據,當固件程序設置68013a的EPx-AUTOINLENH:L為512 B,當ALITOIN=1時68013a將自動以512 B為單位打包傳輸到USB上。在異步傳輸時SLWR用于鎖存總線數據,在同步傳輸時SLWR做為使能信號,在SLWR為低,每個IFCLK上升沿鎖存總線數據,至此完成這個項目的數據流控制設計。

2 結 語

通過以上設計,成功地實現了MT9M112,FPGA和。EZ_USB FX2 68013A之間的通信,該方案將CMOS圖像傳感芯片MT9M112的數據完整地傳輸到PC機,在PC機經數據處理(可選擇提取Y信號或將全部信號),解碼后可得清晰的灰度或彩色圖像。方案通過FPGA的FIFO_Core實現了8位數據向16位數據的轉換,然后利用EZ_USB FX2 68013A Slave FIFO的EP6端口把數據傳給PC機,實現了同步通信。與目前社會上用DSP處理器異步通信相比,利用FPGA不僅降低了成本而且解決了數據傳輸過程中易阻塞的問題,實現了數據無縫傳輸,得到的圖像也更為清晰流暢。

評論