級聯信號處理器的FPGA實現

3 FPGA仿真

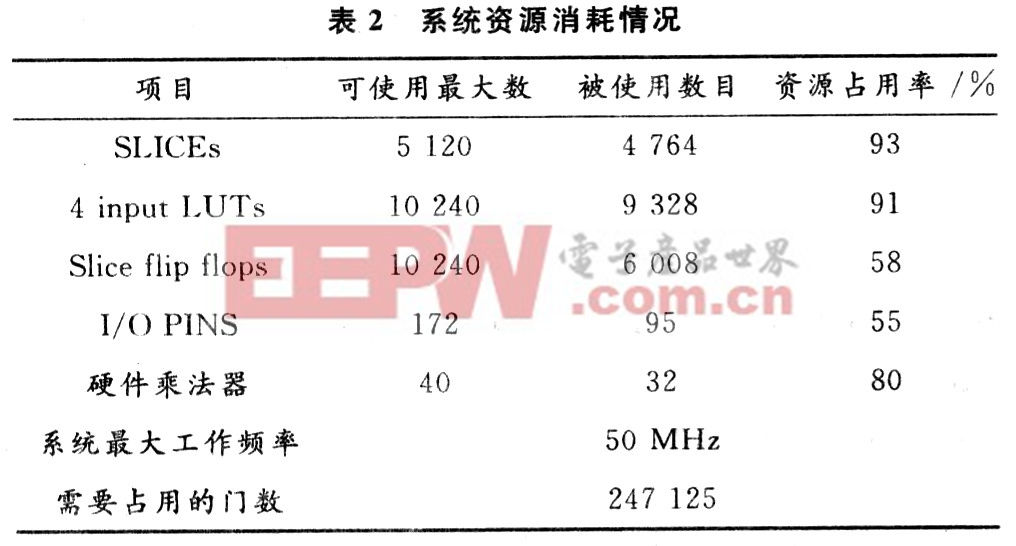

系統利用FPGA實現了一個32階的級聯型信號處理器,選用的FPGA芯片是XILINX公司的集成了18×18位硬件乘法器的VirtexⅡ系列的XC2V1000-5-FG256,其資源消耗情況如表2所示。本文引用地址:http://www.104case.com/article/191993.htm

為了方便仿真和結果觀察,選用固定值輸入,圖4(a)和圖4(b)分別是系統級聯型工作模式及系數切換仿真和系統單片工作模式仿真結果。

從圖4(a)和圖4(b)可以看出,系數寄存器和內部控制寄存器可以正確讀寫,當輸入系數切換指令后,系數正常交換,整個系統工作正常。

4 性能分析

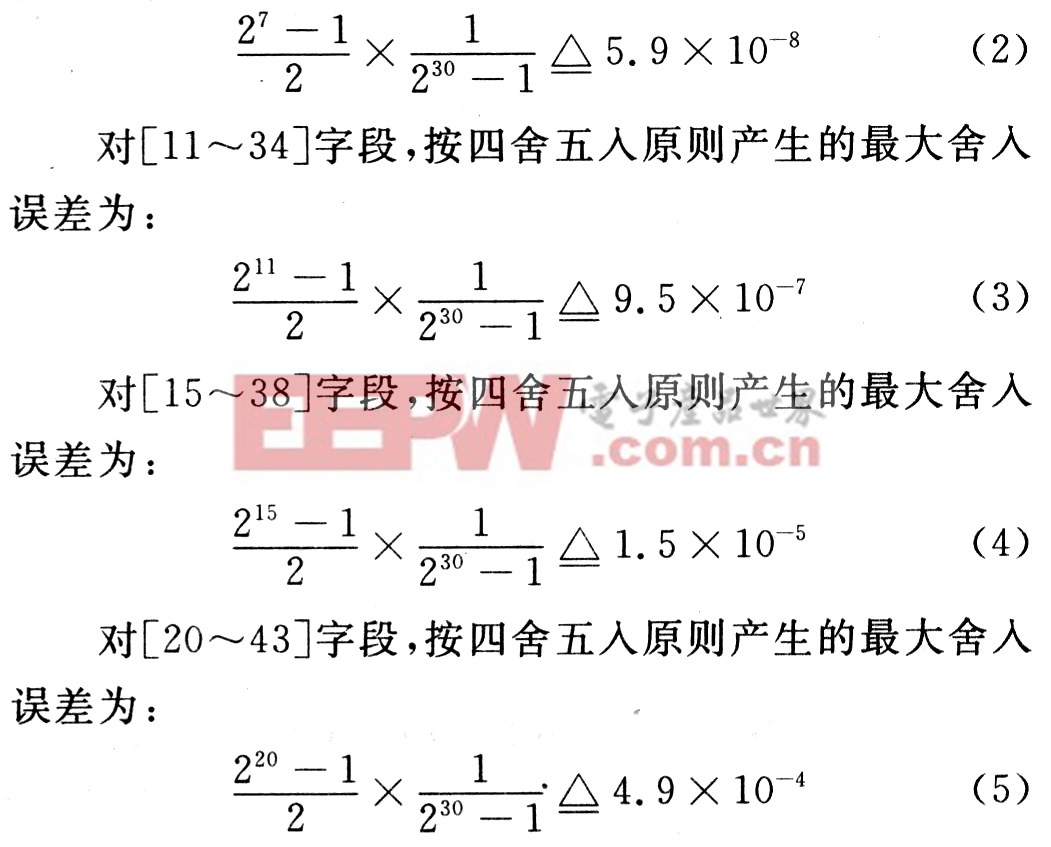

系統的輸入數據和系數都是16位的二進制補碼,所以中間結果的[0~30]字段對應著-1~+1。而系統的中間結果是以滿精度運算的,所以系統輸出的誤差產生于數據選擇單元,四組字段會產生不同的誤差。

對[7~30]字段,按四舍五入原則產生的最大舍入誤差為:

系統的仿真結果和性能分析都表明,系統可正常工作,且最高工作時鐘可達到50 MHz。

5 結語

討論了級聯型信號處理器的FPGA高效實現,通過系統論證、仿真和硬件調試證明,設計方法正確有效,系統功能實現正常且穩定,為FIR濾波、快速傅里葉變換、自適應濾波等應用提供了一條可行之路,其性能可以隨著可編程邏輯器件的發展而不斷提高。

評論