基于FPGA的高階QAM調(diào)制器的實現(xiàn)

用相位累加器輸出的數(shù)據(jù)作為波形存儲器(ROM)的相位取樣地址,這樣就可以把存儲在波形存儲器內(nèi)的波形抽樣值經(jīng)查找表查出,完成相位到幅值轉(zhuǎn)換。ROM設(shè)計的關(guān)鍵問題是進行初始化,就是將正弦波的二進制幅度碼按一定的格式輸入到存儲器初始化(.mif)文件,此文件可以C語言或者Matlab語言程序生成。

DDS系統(tǒng)輸出信號的頻率為f0=fclk×M/2N,頻率分辨率為△f=fclk/2N,當(dāng)M=2N-1時,DDS最高的基波合成頻率為f0max=fclk/2。對于本系統(tǒng),時鐘頻率fclk=155.520 MHz,N取12。仿真結(jié)果如圖4所示。

由于兩個正交本振的形成是通過Madab運算得到的查找表,所以由DDS得到的載頻不存在幅度差異,理論上其正交性也完全可以得到保證,但由于存儲精度的影響,存在量化誤差。

4 系統(tǒng)設(shè)計與仿真

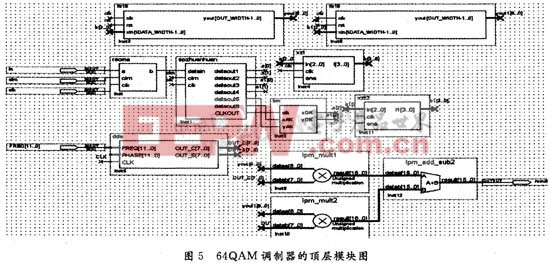

根據(jù)以上各模塊單元的設(shè)計,構(gòu)成64QAM調(diào)制器的頂層文件如圖5所示。運用QuartusⅡ及Matlab軟件實現(xiàn)64QAM調(diào)制器仿真,仿真結(jié)果如圖6所示。

5 結(jié) 語

本文介紹了用FPGA實現(xiàn)全數(shù)字高階QAM調(diào)制器的思想和方法,采用原理圖和Verilog語言,用可編程芯片StratixⅡ系列中的EP2S30F484C3實現(xiàn)了整個設(shè)計,結(jié)果表明符合設(shè)計要求。為進一步的研究和設(shè)計全數(shù)字高階QAM系統(tǒng)打下了良好的基礎(chǔ)。

評論