基于FPGA的高階QAM調(diào)制器的實(shí)現(xiàn)

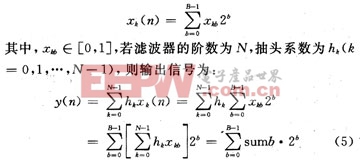

本設(shè)計(jì)采用分布式算法(DA)原理,利用FPGA查找表代替乘法器來(lái)實(shí)現(xiàn)FIR濾波器,其基本思想如下:

假設(shè)輸入信號(hào)數(shù)據(jù)位為B位,則濾波器在n時(shí)刻的第k個(gè)輸入為:

從式(5)可以看出,F(xiàn)IR濾波器中乘加單元的運(yùn)算是算法核心。如果建立一個(gè)查找表(Look Up Table,LUT),表中數(shù)據(jù)由所有固定系數(shù)(h0,h1,…,hN-1)的所有加的組合構(gòu)成(和用sumb表示,6∈[0,B-1]),那么,用N位輸入數(shù)據(jù)構(gòu)成的N位地址去尋址LUT,如果N位都為1,則LUT的輸出是N位系數(shù)的和,如果N位中有0,則其對(duì)應(yīng)的系數(shù)將從和中去掉。這樣乘加運(yùn)算就變成了查表操作。整數(shù)乘以2b可以通過左移6位實(shí)現(xiàn)。

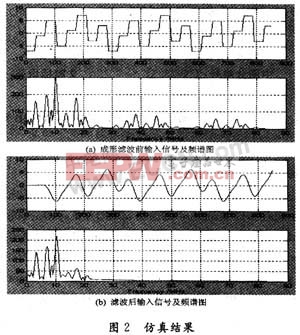

對(duì)于本系統(tǒng),碼元速率為25.92 Mbaud,滾降系數(shù)選取為0.5,抽頭個(gè)數(shù)取N=16,抽頭系數(shù)精度取10 b,輸入數(shù)據(jù)為4 b,輸出精度取9 b。仿真結(jié)果如圖2所示。

從圖2可以看出:碼元速率為25.92 Mbaud的基帶信號(hào)經(jīng)成形濾波后,頻譜被限制在20 MHz范圍內(nèi)。

3.2 正交調(diào)制器的設(shè)計(jì)

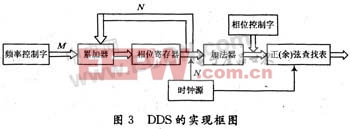

經(jīng)成形濾波后的兩路基帶信號(hào)分別對(duì)DDS(DirectDigital Synthesizer)產(chǎn)生的兩路正交的載波進(jìn)行調(diào)制,然后進(jìn)行矢量相加形成調(diào)制信號(hào)輸出。DDS的FPGA實(shí)現(xiàn)框圖如圖3所示。

DDS的基本原理是利用采樣定理,利用查找表法產(chǎn)生波形。相位累加器是DDS系統(tǒng)的核心部分,每來(lái)一個(gè)時(shí)鐘脈沖,累加器將頻率控制字M與相位寄存器輸出的累加相位數(shù)據(jù)相加,把相加后的結(jié)果送至相位寄存器的數(shù)據(jù)輸入端;相位寄存器將累加器在上一個(gè)時(shí)鐘作用后所產(chǎn)生的新相位數(shù)據(jù)反饋到累加器的輸入端,以使累加器在下一個(gè)時(shí)鐘的作用下繼續(xù)與頻率控制數(shù)據(jù)相加。這樣,相位累加器在參考時(shí)鐘的作用下,進(jìn)行線性相位累加,當(dāng)累加器累加滿量時(shí)就會(huì)產(chǎn)生一次溢出,完成一個(gè)周期性的動(dòng)作,這個(gè)周期就是DDS合成信號(hào)的一個(gè)頻率周期,累加器的溢出頻率就是DDS輸出的信號(hào)頻率。

評(píng)論